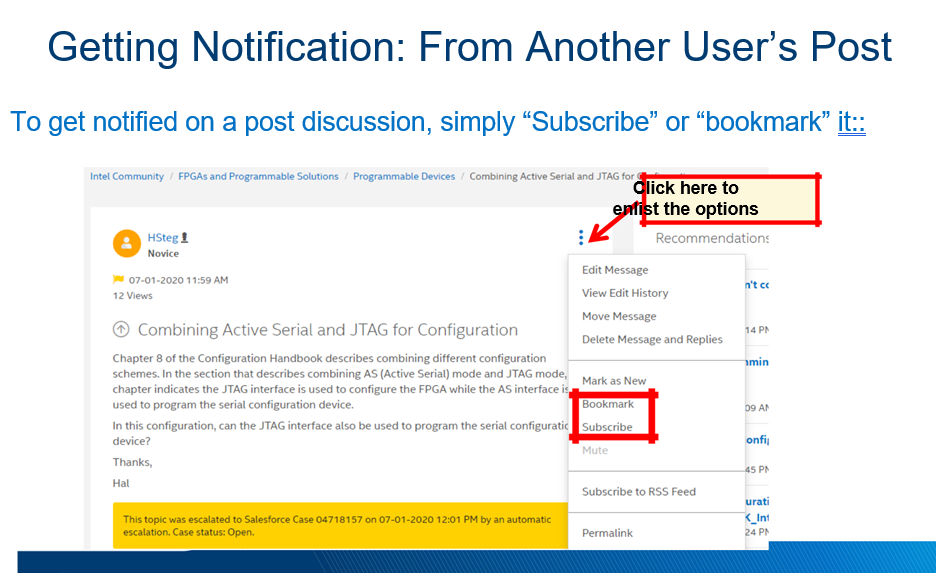

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everyone my name is Paul,

At the moment I'm working on the DE0 nano soc card from Terasic and I'm trying very hard to program a frequency counter, to be clearer, I started to do it but I'm stuck because I don't get not the expected output results.

I come to you for assistance. I will post my vhdl file and the one in c below my question.

Thank you.

library ieee;

use ieee.std_logic_1164.all;

use IEEE.numeric_std.all;

use ieee.std_logic_signed.all;

entity Recepteur is

port (

RSTn : in std_logic;

CLK : in std_logic;

REG : out std_logic_vector(7 downto 0);

INPUT: in std_logic

);

end entity;

Architecture behavior of Recepteur is

signal clear: std_logic := '0';

begin

proc_clear : process(RSTn,CLK,INPUT)

variable val : std_logic := '0';

begin

if RSTn = '0' then

clear <= '0';

elsif (falling_edge(CLK)) then -- front descendant

clear <= '0';

if (INPUT = '1') and (val='0') then

clear <= '1';

end if;

val := INPUT;

end if;

end process;

proc_REG : process(RSTn,CLK)

variable COUNT : natural := 0;

constant MINVAL8 : std_logic_vector(7 downto 0) := "01010000";

constant MINVAL: natural := to_integer(unsigned(MINVAL8));

begin

if RSTn = '0' then

COUNT := 0;

REG <= (others =>'0');

elsif clear = '1' then

if (COUNT - MINVAL) >= 0 then

REG <= std_logic_vector(to_unsigned(COUNT - MINVAL,8));

end if;

COUNT := 0;

elsif (rising_edge(CLK)) then

if (COUNT - MINVAL) < 255 then

COUNT := COUNT + 1;

end if;

end if;

#define soc_cv_av

#define DEBUG

#include <stdio.h>

#include <unistd.h>

#include <stdint.h>

#include <fcntl.h>

#include <sys/mman.h>

#include "hwlib.h"

#include "soc_cv_av/socal/socal.h"

#include "soc_cv_av/socal/hps.h"

#include "soc_cv_av/socal/alt_gpio.h"

#include "hps_0.h"

#define HW_REGS_BASE ( ALT_STM_OFST )

#define HW_REGS_SPAN ( 0x04000000 ) //64 MB with 32 bit adress space this is 256 MB

#define HW_REGS_MASK ( HW_REGS_SPAN - 1 )

//setting for the HPS2FPGA AXI Bridge

#define ALT_AXI_FPGASLVS_OFST (0xC0000000) // axi_master

#define HW_FPGA_AXI_SPAN (0x40000000) // Bridge span 1GB

#define HW_FPGA_AXI_MASK ( HW_FPGA_AXI_SPAN - 1 )

int main() {

//pointer to the different address spaces

void *virtual_base;

void *axi_virtual_base;

int fd;

void *h2p_lw_reg3_addr;

void *h2p_led_addr; //led via AXI master

// map the address space for the LED registers into user space so we can interact with them.

// we'll actually map in the entire CSR span of the HPS since we want to access various registers within that span

//nous allons en fait cartographier l'ensemble de la plage CSR du HPS puisque nous voulons accéder à divers registres au sein de cette plage

if( ( fd = open( "/dev/mem", ( O_RDWR | O_SYNC ) ) ) == -1 ) {

printf( "ERROR: could not open \"/dev/mem\"...\n" );

return( 1 );

}

//lightweight HPS-to-FPGA bridge

virtual_base = mmap( NULL, HW_REGS_SPAN, ( PROT_READ | PROT_WRITE ), MAP_SHARED, fd, HW_REGS_BASE );

if( virtual_base == MAP_FAILED ) {

printf( "ERROR: mmap() failed...\n" );

close( fd );

return( 1 );

}

//HPS-to-FPGA bridge

axi_virtual_base = mmap( NULL, HW_FPGA_AXI_SPAN, ( PROT_READ | PROT_WRITE ), MAP_SHARED, fd,ALT_AXI_FPGASLVS_OFST );

if( axi_virtual_base == MAP_FAILED ) {

printf( "ERROR: axi mmap() failed...\n" );

close( fd );

return( 1 );

}

//the address of the two input (reg1 and reg2) registers and the output register (reg3)

h2p_lw_reg3_addr=virtual_base + ( ( unsigned long )( ALT_LWFPGASLVS_OFST + PIO_REG3_BASE ) & ( unsigned long)( HW_REGS_MASK ) );

printf( "\n\n\n----------- PIO_REG1_BASE -------------\n\n" );

while(1){

printf( "Recepteur REG %d\n", *((uint32_t *)h2p_lw_reg3_addr));

sleep(1);

}

if( munmap( virtual_base, HW_REGS_SPAN ) != 0 ) {

printf( "ERROR: munmap() failed...\n" );

close( fd );

return( 1 );

}

if( munmap( axi_virtual_base, HW_FPGA_AXI_SPAN ) != 0 ) {

printf( "ERROR: axi munmap() failed...\n" );

close( fd );

return( 1 );

}

close( fd );

return( 0 );

}

end process;

end behavior;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry I made a mistake with these 2 lines which appear at the end of the code in C but which are rather lines at the end of the code in VHDL.

end process;

end behavior;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You probably should start a new topic on this and clearly ask your questions separate from your code. Not sure why this is a part of a thread on using the forum.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Siffrediano You need to ask Microsoft what their requirements are, not Intel.

Doc (not an Intel employee or contractor)

[Maybe Windows 12 will be better]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

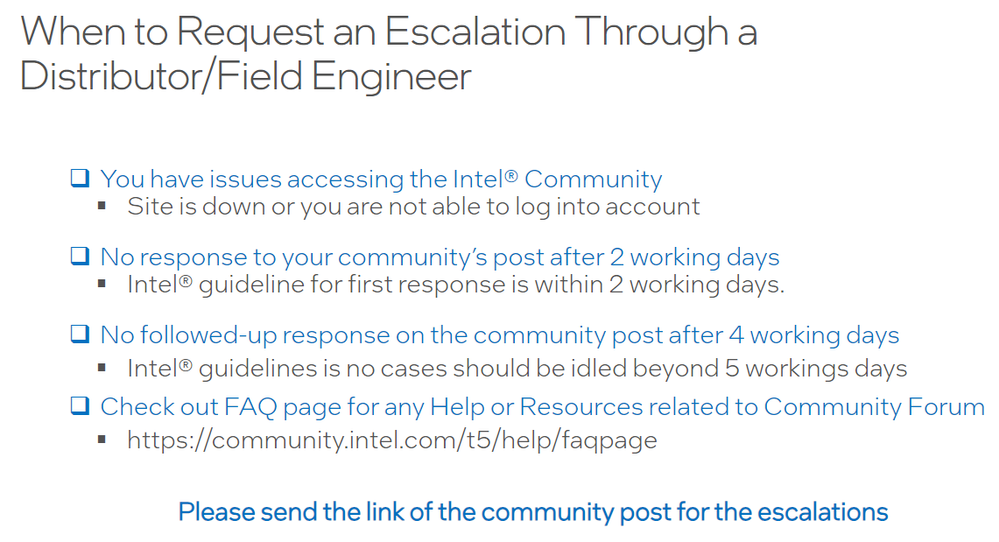

What recourse is there when there is no (first) response to (multiple) Community posts after 14 DAYS?

How does one simply gain access to existing Intel documentation, with a previously completed NDA, but without an assigned field engineer?

What can one do when Intel denies Premier Support on corporate accounts, and dodges Customer Service requests?

After months of frustration, the only solution I can see is to strongly recommend to our own clients that they fully avoid using Intel FPGAs in their designs. Other vendors provide greater functionality, fuller documentation, and avoid this nonsense.

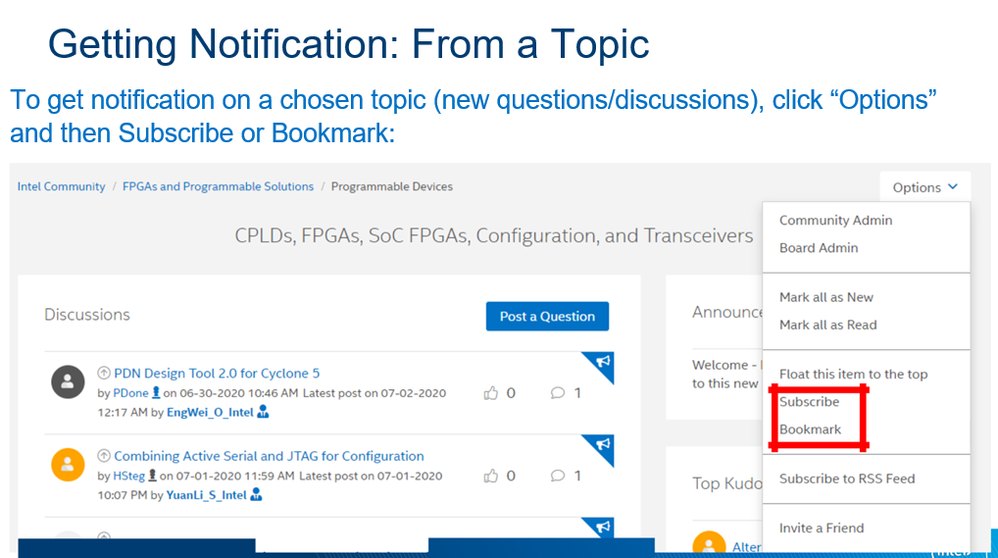

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page