- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using the 10AX048H4F34E3SG device with 130 LVDS data pairs connected. The LVDS pins are distributed over 6 IO-banks.

All pins feed to a GPIO primitive (ddr mode). The clock for the GPIO comes from the PLL in the same IO-bank. For a group of signals I want use 8 clock outputs of that PLL for a dynamic phase shift.

To realize phase shift for all 130 pins I want to use 34 different clocks which feeds the full rate clock input of the GPIO.

During fit Quartus produce some errors:

The Fitter cannot place 1 auto-promoted clock driver, which is within IOPLL Intel FPGA IP sen_pll_altera_iopll_181_qprrpya

Error (177032): Section clock (SCLK) network in spine clock region bounded by (109,0) and (148,31) is congested due to limited connectivity

Info (18630): This congestion may be avoided by moving or disabling promotion of any of the following competing signals:

Info (175030): Unroutable signal:

Info (175026): Source: auto-promoted clock driver deserializer:DESER|sen_pll:SENPLL_3|sen_pll_altera_iopll_181_qprrpya:iopll_0|altera_iopll:altera_iopll_i|twentynm_iopll_ip:twentynm_pll|outclk[2]~CLKENA0

I have done a second run with that constraint:

set_instance_assignment -name GLOBAL_SIGNAL OFF -to "deserializer:DESER|sen_pll:SENPLL_3|sen_pll_altera_iopll_181_qprrpya:iopll_0|altera_iopll:altera_iopll_i|twentynm_iopll_ip:twentynm_pll|outclk[2]~CLKENA0

But there is no effect. The error remains. I also tried to switch off the Auto Global Clock option in the dvanced Fitter Settings but the error remains.

Why is it not possible to use all clock outputs of a PLL? When I reduce the number of clocks than fitting is successfully.

Jens

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The tool is only showing you the clock that could not be routed. You probably need to take more clocks off of the global routing channels to free up resource usage. Check the Compilation Report to see which clocks (or potentially high fanout control signals) are using the global clocks and see if you can remove more of them.

I'm not sure why turning off the Auto Global setting causes the same issue, but turning that off means that you would need to manually specify which clocks should use the global routing channels.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I checked the report (congestion summary in Fitter report) and tried to remove all clocks.

But the error remains. It seems the fitter do not recognize my assignments.

assignment:

-name GLOBAL_SIGNAL OFF -to "deserializer:DESER|sen_pll:SENPLL_6|sen_pll_altera_iopll_181_qprrpya:iopll_0|altera_iopll:altera_iopll_i|twentynm_iopll_ip:twentynm_pll|outclk[3]~CLKENA0"

fitter:

Info (175026): Source: auto-promoted clock driver deserializer:DESER|sen_pll:SENPLL_6|sen_pll_altera_iopll_181_qprrpya:iopll_0|altera_iopll:altera_iopll_i|twentynm_iopll_ip:twentynm_pll|outclk[3]~CLKENA0

What can I do more?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jen

Are you able to share you sample design?

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jen

Have you try to use ALTCLKCTRL IP to route your clock to regional clock?

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eng Wei,

no. It seems to me that Quartus have no problem to route the global clock to regional clock. But there are not enough ressorces to connect all PLL outputs in that region.

Jens

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jens

Sorry for late response as I have just back from the extended holiday. Let me take a look on the attached design.

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jens

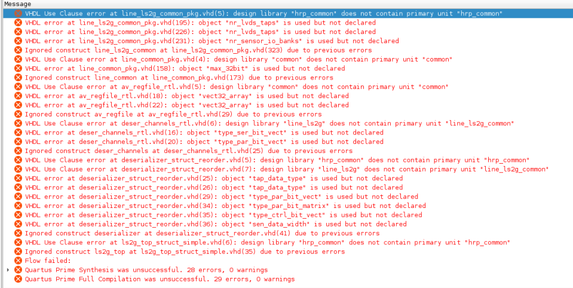

I am using Quartus Pro Version 18.1.1 which is the one shown up in qsf. Looks like some IPs are created based on older Quartus version, so I upgraded the IPs by Auto Upgrade. But I am getting a couple of errors. What is the workaround to avoid those front end compilation error?

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eng Wei,

I don't know why Quartus does not put this package (hrp_common) and some other files in the archive. I will check that and send you a new one.

Jens

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I unpacked the archive with Quartus and start a compilation. I couldn't see any errors. The package hrp_common is already included in archive. (see files_ls2g_simple.jpg)

The synthesis was running without errors (see log1.jpg)

Please check the files in Quartus Project Navigator.

Jens

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jens

The file list looks exactly the same. Perhaps the content of the files changed after I upgraded the IPs. I am using Quartus Prime Version 18.1.1 Build 263. How to avoid this issue when upgrading the IP?

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eng Wei,

I'm using Quartus 18.1.0 Build 625. May be you don't need an update. If you rebuild the qsys after an update you will need some custom components. (see attachment)

Please let me know if this helps.

Jens

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jens

I am able to compile your design now. Let me check on those errors and get back to you.

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jens

The congestions seems to be around bank 3C and 2J. I removed the pin assignment at 3C and the fitter seems to assign those pins to 3F and it is able to pass the full compilation. But we have to take notes on the timing due to the changes.

thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eng Wei,

the PCB is already manufactured. Bank 3F is used for the DDR4 interface. Almost 100% of the pins are assigned. Removing pin assignments is not an option

Jens

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jens

If that is the case, you need to use the Chip Planner to view the congested region. You may also attempt to reduce the clock network usage in the design, either by using fewer clocks, or by using smaller clocks instead of larger clocks. For example, you can use regional clocks instead of global clocks where possible.

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eng Wei,

If I reduce the number of clock outputs from each PLL and distribute them across the DDR I / O, fitting is successful.

In this case, however, it is not possible to compensate for the clock skew of all 128 I / O, which is done by dynamic phase shifting.

It would be fine if I could use all of the clock outputs from each PLL in 6 I / O banks. A reduction of clocks is possible, but does not work to reduce the clock skew in all data channels.

Jens

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jens

Are those 128 I/Os mentioned having clock relationship among them? If yes, is that possible to use fewer promoted GCLK from only certain number of PLL output clocks? Another suggestion is whether we can create clock divider logic to generate clocks from GCLK? With that, those clocks are coming from the same source which have dynamic phase shifting.

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eng Wei,

Yes they have. I've tried with fewer PLL outputs. The fitting is successful, but the data alignment is not. The manufacturer of our sensor uses a Xilinx FPGA for the demonstrator.

With the Xilinx it is possible to shift the phase for each of the 128 input data bits.

Inside the Arria device, I can only use dynamic phase alignment for a group of input pins in conjunction with a static input delay (using INPUT_DELAY_CHAIN).

However, this method is not sufficient to align all 128 data bits.

Jens

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jen

Can you share with us a block diagram on what you are trying to achieve with your design and what's the requirement such as data rate, performance and etc?

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, there is no block diagram. However, you can use the sample project that was provided in my previous posts.

I'm trying to use a DDIO with half rate logic for each LVDS channel (128 in total) to convert it to a single data rate. The channels represent sensor data bits. These bits have a skew of up to one DDR clock period. For the bit alignment I have to shift the data bits. That's why I use clocks with different phase shifts as the input clock for the DDIO.

The DDR clock rate is 500 MHz

Jens

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page