- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is there an 10GE example design available for A10 Device ? We need this to verify 10GE Serdes Functionality on A10SOC board.

Also I'm not very familar to 10GE testing method, so if some recommendation method to verify 10GE works OK or Not, which wouldbe helpful very mucch.

Thanks a lot

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

You may refer to the following link for the Arria 10 Low latency 10G MAC example design. This should be helpful for you to use it as the starting point for your design development.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-20016.pdf

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @SengKokL_Intel ,

Sory but I'm really a newbie to FPGA world!!

I have checked the ug-20016 "4. 10GBASE-R Ethernet Design Example for Intel Arria 10" ,and tried to generate an design example using the Platform Designer (with Quartus Pro 19.2).

And this generated project can be compiled ok in Quartus Pro 19.2. But in Platform designer, I select "No development kit" option.

I have a Intel A10SOC Evaluation Board on hand, and If I wanto run my 10GE test project on it ? HOw should I do in next step ?

( I guess I should assign the correct pin-assignmnt in my project according to A10SOC Board, anythings else ? )

Thanks in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello SK, thanks for guidance, :) May I ask a more question ?

I follow "ug-20016.pdf" to generate a "10GBASE-R Ethernet Design Example" for Arria 10" in Platform Desigher ( Pro 19.2) , and in Target Board field, I select " GX Transceiver Signal Integartion Development KIt ", I can generate example and compile it OK. Then I open the “altera_eth_top.qsf" to check what's its appropriate Pin Assignment ?

I dowload schematics from "Arria 10 GX Transceiver Signal Integrity Installation Package (Production Edition)" from link: https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/dev-kits/altera/kit-a10-gx-si.html, But I found some discrepancy.

1) in Design Example "altera_eth_top.qsf ", the SFP+ connector pin assigns are below, : PIN_BC7、AW7 , _BD5、_BA7 ,

set_location_assignment PIN_BC7 -to tx_serial_data[0]

set_location_assignment PIN_AW7 -to rx_serial_data[0]

set_location_assignment PIN_BD5 -to tx_serial_data[1]

set_location_assignment PIN_BA7 -to rx_serial_data[1]

2) But from the schematics of " A10 GX Transceiver Signal Integartion Board" and its user guide, the SFP+ PIN is obvious diferrent :

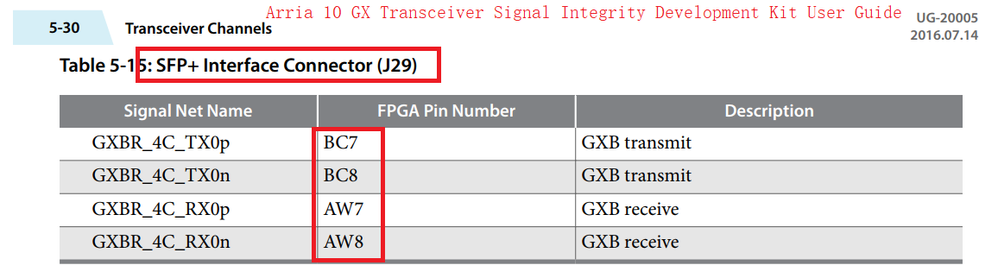

Table 5-15: SFP+ Interface Connector (J29)

Signal Net Name Pin Number Description

GXBR_4C_TX0p BC7 GXB transmit

GXBR_4C_TX0n BC8 GXB transmit

GXBR_4C_RX0p AW7 GXB receive

GXBR_4C_RX0n AW8 GXB receive

SO WHY THE example pin assignment are different to Board Shcematics ? What's the problem hete ? Thanks in advance .

/Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SK,

I upload the example *qsf as well, in case you want to double check it if possbile. Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, you are right. There is no pin assignment if no development kit was selected, hence the user needs to assign the correct pin assignment accordingly.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This is correct for channel 0, this is same as TX0p and RX0p, for TX0n and RX0n, the Quartus will auto-assign, and you can find it from the Fitter report -> Plan Stage -> Input Pins /output Pins,

set_location_assignment PIN_BC7 -to tx_serial_data[0]

set_location_assignment PIN_AW7 -to rx_serial_data[0]

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @ SK , get it.

I just wonder SI Board has only one SFP+ hardware interface, but the Example generate two SFP+ i/f , which introduce a bit confusion. Anyway I understand yet.

Thanks for quick response

best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @SengKokL_Intel ,

May I ask another more question. Thanks in advance.

I just generated another LL 1G/10G MAC Example , I select " GX Transceiver Signal Integartion Development KIt ", but I found in its *.qsf , there're below :

"

set_instance_assignment -name IO_STANDARD "HSSI DIFFERENTIAL I/O" -to tx_serial_data[*]

set_instance_assignment -name IO_STANDARD "CURRENT MODE LOGIC (CML)" -to rx_serial_data[*]

set_instance_assignment -name XCVR_VCCR_VCCT_VOLTAGE 1_0V -to tx_serial_data[*]

set_instance_assignment -name XCVR_VCCR_VCCT_VOLTAGE 1_0V -to rx_serial_data[*]

"

My wonder is in this example design, why "tx_serial_data[]" uses ""HSSI DIFFERENTIAL I/O", but the "rx_serial_data[]" uses "CURRENT MODE LOGIC (CML)" ?

Should they use the same IO_STANDARD, maybe LVDS or CML ? it's strange ..

Thanks

/Jet

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jet,

You can find the answer from the forum thread below:

https://forums.intel.com/s/question/0D50P000043ncdzSAA/difference-between-cml-and-high-speed-differential-io-transceiver-io-standard

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page