- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

in my design I am implementing an OpenRISC processor that is connected to an onboard SDRAM. I have included a PLL that outputs 2 clocks, both of them 60 MHz and of the same phase:

clk_sys --> the clock of the processor and the bus paripherals.

clk_sdram --> the clock of the SDRAM and the SDRAM controller.

As you can see from the above I am passing the SDRAM clock generated at the PLL, to the clock pin of the SDRAM. For this I am using the following command in my SDC:

# SDRAM clock at the FPGA pin

create_generated_clock -name clk_sdram -source [get_pins $pll_pin0] -duty_cycle 50/1 [get_ports {sdram_clk_pad_o}]I am also constraining the delay of this clock-out pin with the following commands in my SDC:

# PLL to FPGA output (clear the unconstrained path warning)

set_min_delay -from $pll_pin0 -to [get_ports {sdram_clk_pad_o}] 1

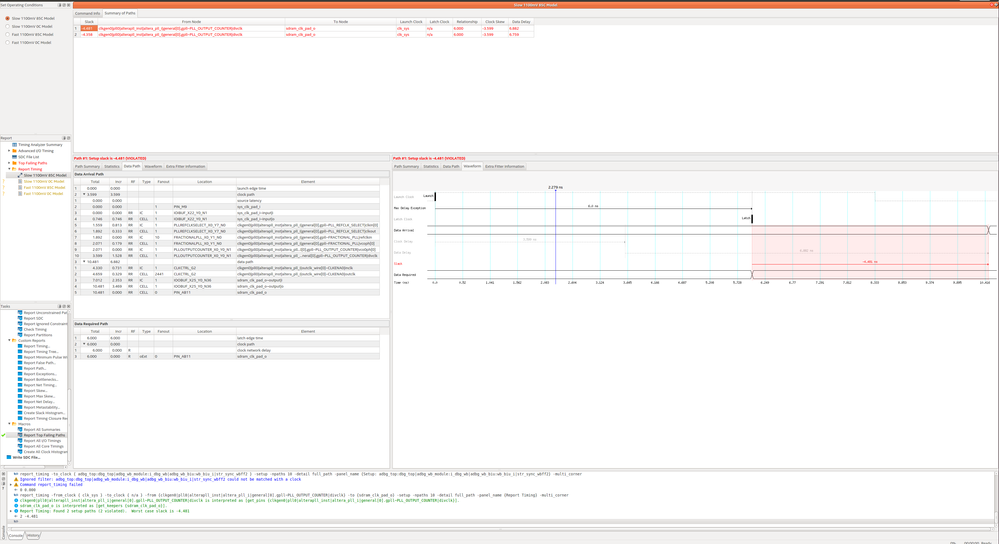

set_max_delay -from $pll_pin0 -to [get_ports {sdram_clk_pad_o}] 6After the compilation is finished I get a Setup violation on this path from the FPGA to the clock-out pin (see photo attached). The setup slack is -4.481ns. As I said the period for this clock which is 60 MHz is 16.667ns.

From what I see in this path there is no complex combinational logic included. After it exits the PLL the signal enters an IOBUF with the name "IOOBUF_X25_Y0_N36" and then straight to the output pin.

I also saw in the Chip Planner that the PLL generating the signal is the closest one to the output pin.

What can I do in order to solve this setup slack?

Would multi-cycle by 2 give a solution to this problem?

I am using a Cyclone-V board and Quartus Prime 19.1 Standard Edition.

Thank you in advance for your responses.

Kind regards,

anm

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Output clocks should have false path timing exceptions on them. The failed analysis you are seeing (that screenshot is way too small; can hardly read anything in it) is as if the output is a data path, which it isn't.

As such, you also don't need the set_min_delay and set_max_delay constraints. This is a clock, so it is used as a reference for clocking the external device, not for meeting path delay in the FPGA.

Is $pll_pin0 the input reference clock of the PLL or the output clock pin? It should be the output pin. And you should not have the duty_cycle option in there either. Just do a derive_pll_clocks instead which handles the creation of both output clocks from the PLL. So you should have after all this (assuming $pll_pin0 is the output clock pin of the PLL for clk_sdram):

create_clock -period <period> -name <input clock name> [get_port <input clock port>]

derive_pll_clocks

create_generated_clock -name clk_sdram -source [get_pins $pll_pin0] [get_ports {sdram_clk_pad_o}]

set_false_path -to [get_ports {sdram_clk_pad_o}]

Let me know if that helps.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @sstrell,

thanks for the reply, due to the maintenance of the forums I wasn't able to post earlier.

Yes the $pll_pin0 is the output clock pin of the PLL. One strange thing is that in Quartus I configure the PLL to have two clock outputs, on for the system clock and one for the sdram clock (in order to have smaller fan-out) and both of them are configured to be the same frequency (60 MHz) and have the same phase. But when I apply the "derive clocks pll" in my SDC file, Quartus uses for both the same PLL clock output pin to do timing analysis. I suppose this doesn't make any difference, for the reasons I mentioned above (same frequency, same phase).

For the moment I am not applying a false path on the generated clock but I am not sure if I should indeed false path it or not. The clock used to generate this clock, before reaching the output port "sdram_clk_pad_o", it is used also to clock the Controller of the SDRAM. Actually the controller of the SDRAM gets both the system clock and the clock destined for the SDRAM. What do you believe on this? Should a false path on the generated clock affect it?

Also I did some search the last couple of days and came up with the following on how to constraint my Source Synchronous interface with the SDRAM:

set clk_sdram_period 16.6667

#**************************************************************

# SDRAM Constraints

#**************************************************************

## SDRAM timing parameters from Datasheet

##

## From Datasheet: DATA, ADDRESS, CKE, CS, RAS, CAS, WE, DQM all have

## the same setup/hold time

##

## DATA tco(min) = tOH, tco(max) = tAC

set sdram_tsu 1.5

set sdram_th 0.8

set sdram_tco_min 2.7

set sdram_tco_max 5.4

# FPGA timing constraints

set sdram_input_delay_min $sdram_th

set sdram_input_delay_max [expr {$clk_sdram_period - $sdram_tsu}]

#set sdram_input_delay_max [expr {-$sdram_tsu}]

set sdram_output_delay_min $sdram_tco_min

set sdram_output_delay_max $sdram_tco_max

# FPGA outputs to SDRAM

set fpga2SDRAM_outputs [get_ports {

sdram_a_pad_o[*]

sdram_ba_pad_o[*]

sdram_cas_pad_o

sdram_cke_pad_o

sdram_cs_n_pad_o

sdram_dq_pad_io[*]

sdram_dqm_pad_o[*]

sdram_ras_pad_o

sdram_we_pad_o

}]

# FPGA inputs from SDRAM

set SDRAM2fpga_outputs [get_ports {

sdram_dq_pad_io[*]

}]

# Set Output Delay

set_output_delay -clock clk_sdram -max $sdram_input_delay_max $fpga2SDRAM_outputs

set_output_delay -clock clk_sdram -min $sdram_input_delay_min $fpga2SDRAM_outputs

# Set Input Delay

set_input_delay -clock clk_sdram -max $sdram_output_delay_max $SDRAM2fpga_outputs

set_input_delay -clock clk_sdram -min $sdram_output_delay_min $SDRAM2fpga_outputs

The scheme for the clocking of the SDRAM is depicted in the page 21 of the attached pdf.

As you can see on the diagram the setup time for the outputs of the FPGA (inputs to SDRAM) is the tCMS, which is the sdram_tsu in my SDC. This is 1.5 ns and the clock of the SDRAM is 60 MHz (16.6667 ns period).

I am troubled on what I should use in the "set_output_delay -max" option:

A) the -$sdram_tsu which is -1.5ns

B) the {$clk_sdram_period - $sdram_tsu} which is 16.667 - 1.5 = 15.167ns

C) whichever of the above I use are the same constraint

Can you provide your help on this?

Thank you in advance on your response and time.

Kind regards,

anm

p.s. for my previous post if you download the pic and open it, it has a clear and high resolution since it is a screenshot from a 3840 × 2160 screen. If you open it through the forum, it tends to make it smaller in order to fit it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anm,

You may refer to Figure 10 and formula in Example 12

set_output_delay -clock clkB_virt \

-max [expr $CLKBs_max + $tSUb + $BDb_max - $CLKBd_min] \

[get_ports {data_out}]

Thanks.

Best regards,

KhaiY

- Tags:

- i Anm

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any questions?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @KhaiChein_Y_Intel ,

I have been working on some other issues. Sorry for being quiet.

I will check on your solution and get back to you. Thank you!

Kind regards,

Nassos

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page