- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

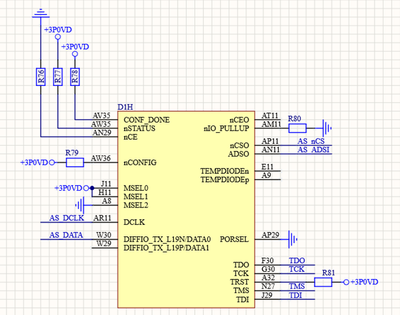

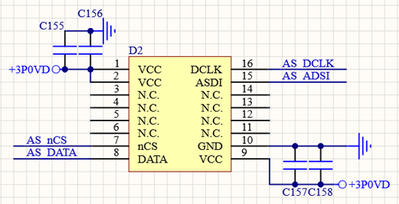

FPGA: Stratix IV (EP4SGX230KF40I3),EPCS: EPCS128

The above two pictures are the standard FPGA configuration methods I found, which are consistent with the officially recommended configuration methods(JTAG+AS).

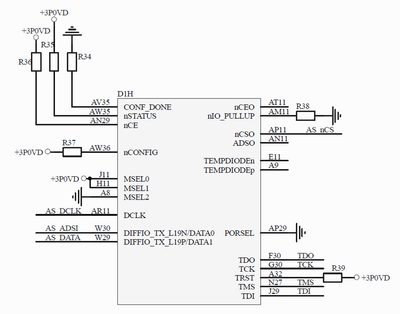

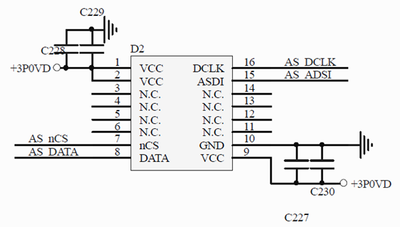

The following two pictures are the FPGA configuration method of a circuit board I found, which is inconsistent with the officially recommended configuration method.I don't know what configuration method this is, and I didn't find the corresponding one in the official manual.

I found out that this way of configuration supports configuring sof/jic files.

Can you tell me what is the configuration of this? Can you elaborate on the features of this configuration? Does this configuration method support remote configuration upgrade? If it is not supported, can it be set in software to accomplish this?

Thank you so much!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The MSEL is still 011, so this is still fast AS. Without looking at the data sheet, perhaps those DATA0/DATA1 pins are dual purpose and can act as ASDI. In other words, this probably has the same features supported by fast AS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, in the second set of schematics CONF_DONE is pulled low and nCE is pulled high.

Both opposite to standard practice. In fact never seen this done before.

So I'm not convinced the second schematic is even functional for configuration via EEPROM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page