- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everyone.

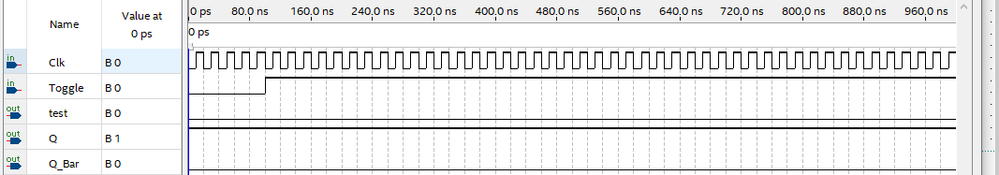

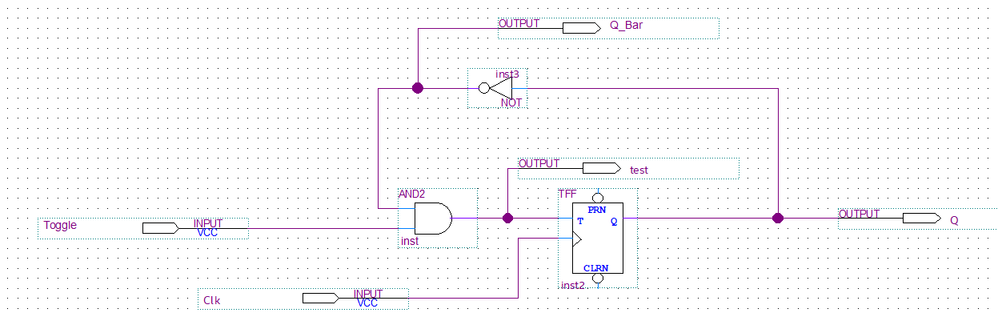

I made a circuit like this.

The TFF has triggered before the "Toggle" single rise up.

I use Quartus FPGA lite 18.1 and 19.1. The simulation is same.

I tried to program it to fpga dev board(EPM240T100C5N). The situation is also same.

I asked this problem to our school teachers.They also can't solve this problem.

I wanna know why the TFF is triggered to high before Clk and "test" signal at the start time.

So what the circuit problem is? Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your input to the flip-flop is low because you're ANDing the high Toggle and the low Q_Bar, so the flip-flop doesn't toggle.

https://en.wikipedia.org/wiki/Flip-flop_(electronics)#T_flip-flop

#iwork4intel

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your input to the flip-flop is low because you're ANDing the high Toggle and the low Q_Bar, so the flip-flop doesn't toggle.

https://en.wikipedia.org/wiki/Flip-flop_(electronics)#T_flip-flop

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I Know the TFF is triggered to high and then it can't not be toggle again.But the TFF is not trigger by CLK or "test" signal.It toggle automatically at the start time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm not sure I understand what you are saying here. As suggested, if you used an OR gate instead of an AND gate, it would work.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There is low toggle resulted by AND gate as high input toggle and low q_bar

Change it to OR gate to make it toggle.

Thanks,

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page