- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

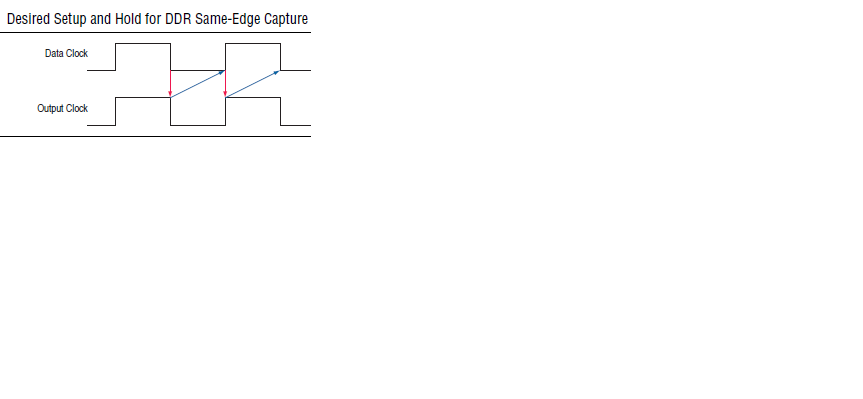

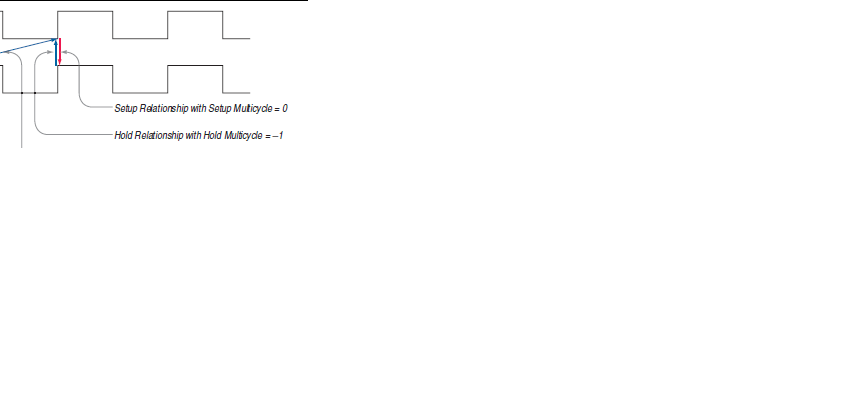

Hi. I have the difficulty to understand the different of set_multicyle_path in system approach and skew approach(FPGA centric) in AN433 doc.

http://www.altera.com/literature/an/an433.pdf

the constraint for system centric approach(pg14),

set_multicycle_path -setup -end 0 -rise_from [get_clocks

data_clock] -rise_to [get_clocks output_clock]

set_multicycle_path -setup -end 0 -fall_from [get_clocks

data_clock] -fall_to [get_clocks output_clock]

the constraint for FPGA centric approach(pg26),

set_multicycle_path -setup -end 0 -rise_from [get_clocks

data_clock] -rise_to [get_clocks output_clock]

set_multicycle_path -setup -end 0 -fall_from [get_clocks

data_clock] -fall_to [get_clocks output_clock]

set_multicycle_path -hold -end -1 -rise_from [get_clocks

data_clock] -rise_to [get_clocks output_clock]

set_multicycle_path -hold -end -1 -fall_from [get_clocks

data_clock] -fall_to [get_clocks output_clock]

Questions:

Why does the FPGA centric approach have extra 2 set_multicyle_path -hold compare to system approach?

I update some as following:

since the two way have different set_false_path later in AN433,

-hold rise->fall,fall->rise for FPGA-centric;

-hold rise->rise,fall->fall for system-centric.

but all the constrain(multipath+false path) will introduce different desired setup/hold relationship.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

FPGA-centric means it's contained within the device itself. As such, the hold analysis happens at the same edge at the boundary of the FPGA as opposed to 1 cycle earlier which is where it would be for the "downstream" device. I would stick with the system-centric approach. It's easier to understand and implement. You can see a good explanation of AN433 in the associated online trainings:

https://www.intel.com/content/www/us/en/programmable/support/training/course/ocss1000.html

https://www.intel.com/content/www/us/en/programmable/support/training/course/oddr1000.html

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

sstrell,

thanks for your response,but I still can not understand it.No matter fpga-centric or system-centric,the desired setup/hold relationship(data_clock and output_clock) should be the same.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page