- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

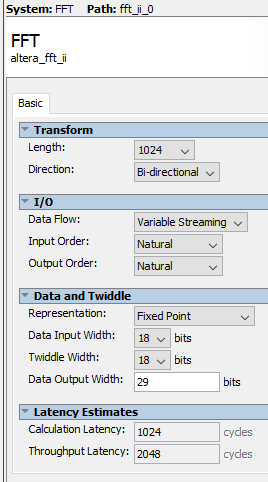

I am using Quartus 22.1 (the problem was in 21.1 the same). IP configuration is attached.

The first anomaly:

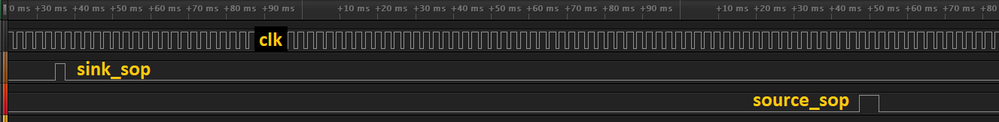

sink_sop and sink_eop are every 128clk, but the source_sop and source_eop are randomly. Sometime every 127clk, sometime 128clk. Is it normal?

Input data are 0x0...0x3FF, sinus. But the output is not repeatable.

I am using BeMicro Max10 with 10M08, it is a small for bigger FFT. But in our project is 10M50, it is bigger. But for testing and pinning is better for me demoboard..

I tried sampling the input data and then inserted to Matlab and the FFT output was OK.

My first example for my project was (only first half with FFT):

https://community.intel.com/t5/FPGA-Wiki/DSP-Basic-Design-Examples/ta-p/735472

I checked the edges and they should be correct according to the datasheet and the example.

I am doing something wrong? Is the problem in the configuration?

Thank you, Tomas

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you please share your project(.qar) with below details.

1) Which Operating system you are using?

2) Which Quartus Software version you are using?

3) Which device(OPN) you are targeting?

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1) Which Operating system you are using - Windows (10 and 11)

2) Which Quartus Software version you are using - Quartus Prime Standard 22.1

3) Which device(OPN) you are targeting - BeMicro Max 10 FPGA KIT (from Arrow), with 10M08DAF484C8GES

My qar is attached.

Thank you, Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

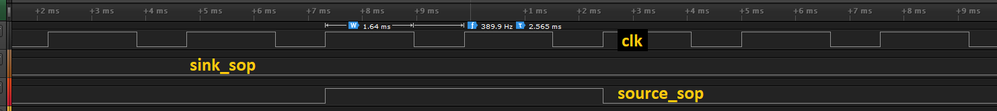

I tried differet FFT settings and different FPGA size.

FPGA: 10M25SAE144I7G

Now, I have another, but similar, problem. The signal source_sop has double size (it takes two clocks of clk). Is it normal?

ZOOM:

What could be the cause? Has the clk signal any restrictions? My clk frequency is 390 Hz.

Thank you, Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you please tap the source_valid as well because source_sop is only valid when source_valid is asserted.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thank you.

The source_valid has ever one low-puls between sink_sop and sink_eop. But low puls is not synchronously with the sink_sop/eop and not synchronously with the source_sop/eop (low puls moves slowly).

What can it do?

reset_n, sink_valid, sink_error, sink_imag, ftpts_in, inverse and source_ready are continually set...

Thank you, Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tomas,

Can you please try the FFT Example Design and share your results.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Goel,

what does it mean "FFT Example Design". Do you have some link, please? Or project?

Thank you, Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tomas,

Please click on the highlighted option, "Generate Example Design" in the IP Parameter Editor.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tomas,

Any update on this.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tomas,

As we do not receive any response from you on the previous answer that we have provided. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

Thank you

Kshitij Goel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page