- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I am working on the tutorial and get stuck at the master_write or master_read command line. I'm using the Quartus Prime Lite 19.1 and Platform Designer (formerly Qsys), I wrote those line command in TCL console in System Console and get the error saying the transaction is taking longer than 10 seconds and continue for another 50 seconds, then it said the system console is giving up. I tried everything to rectify the problem like correcting the path for the environment variable, update to latest Quartus Prime (on having the problem I used version 18.1). Is there any specific set up before using the command line that I need to set in my computer? Any helps are indeed great.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Syed,

Could you provide any possible error message(s) for me to understand better the scenario. Also, which part from the doc you wrote the command tcl in system console that you were mentioning?

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

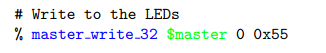

Figure 1

Hi Syafieq,

So here are another 3 links that applied the same JTAG to Avalon M Bridge. Basically it is the same with the JTAG to Avalon MM Bridge.pdf (attached in question post). And I am having the same problems at the same steps.

In the pdf tutorial, as in Figure 1, when I tried to run the command, it shows

"java.lang.Exception: master_read_32: This transaction did not complete in 60 seconds. System Console is giving up."

And in link (3),under Exercise the On Chip RAM, when I tried wrote

"master_read_32 $c_path $ocram 1" same error show up.

(2) https://www.i1ntel.com/content/www/us/en/develop/articles/build-a-custom-hardware-system.html

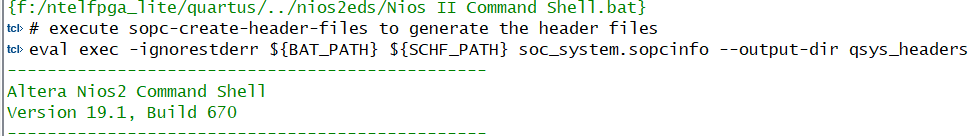

I think it came from the part where I cannot create the header file in (2), because I run below code

"# execute sopc-create-header-files to generate the header files

eval exec -ignorestderr ${BAT_PATH} ${SCHF_PATH} soc_system.sopcinfo --output-dir qsys_headers"

The only things came out is

In link (2), it said using the tcl console in the Quartus, under Generate the Header Files section , I need to create the header file but when I tried to run code in line 21, it shows errors about "invoke while executing"

p/s Hope my reply can make you clear of what I am facing now.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sayed,

I sent you a zip file containing tutorial related to write and read avalon mm using jtg to avalon master bridge via email. You can take a look at it.

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SyafieqS_Intel , I'm using jtag-mm-bridge in my project now, would you please send me a copy file of " tutorial related to write and read avalon mm using jtg to avalon master bridge ..."

Thanks in Advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Attached file has several tutorials for debugging using System Console, Signaltap and ISSP. Hopefully it might be helpful :) @3000021845821.562225903895492E12

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @SyafieqS_Intel ,

I see that this thread is a couple of years old. However, could you send me these zip with the tutorials? It would be really useful for me.

Thanks in advance and regards,

Enrico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do all the previous commands (before master_write_32) run successfully with no warnings or errors? That error usually indicates that System Console can't access the service type (master) that you've set up with the get_service_paths command. Also note that the open_service command is deprecated and that claim_service should be used. I don't think open_service will cause an error, but it should not be used anymore.

It would also be helpful to see your Platform Designer system and how the JTAG to Avalon bridge is connected and how the addressing is set up.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello there,

So I am following this tutorial

Everything can easily followed but up until "Generate header file", I started getting error when I tried to enter this command line

BAT_PATH {}

tcl> if {$tcl_platform(platform) == "windows"} {

> set BAT_PATH [glob -join $quartus(quartus_rootpath) .. nios2eds {Nios II Command Shell.bat}]

> }

Alternatively it worked when I generate it using NIOS II shell but the problem is for the next line where there is need for global join

# execute sopc-create-header-files to generate the header files

tcl> eval exec -ignorestderr ${BAT_PATH} ${SCHF_PATH} soc_system.sopcinfo --output-dir qsys_headers

# read the header file for master_0 into a TCL variable

tcl> set master_0_header [read [open [glob -join qsys_headers master_0.h] r]]

I cannot find any suggestion on the web so I proceed with the next tutorial in this link

When I tried to insert master read and write command, the error said

"Jun 01, 2020 8:04:30 PM com.altera.debug.coreWARNING: This transaction has not completed in 10 seconds. System Console will keep trying for 50 more seconds.

----after 50 seconds----

java.lang.Exception: master_read_32: This transaction did not complete in 60 seconds. System Console is giving up.

Someone told me that it is because of the IP (JTAG to Avalon) is not responding and the clock is missing.

Can you advice me on this? Here I attached the Platform Designer .qsys that I worked on based on the links above. Thanks

Regards

Sayed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page