- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everyone,

I am trying to run simulation for the 25g Ethernet IP for startix fpga with fpga number 1SGO85HN2F4312VG. As per @https://www.intel.co.jp/content/www/jp/ja/programmable/documentation/gkr1505413442088.html#ezc1519265402640 I am running the simulation on modelsim. I am facing some issues in running the script.

The error message that I recieve is:

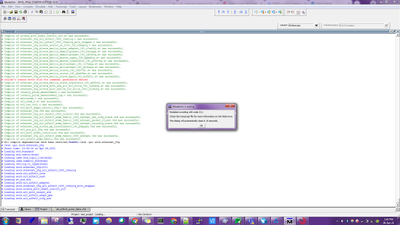

# do run_vsim.do

# ** Warning: (vlib-34) Library already exists at "work".

# basic_avl_tb_top

# C:\intelFPGA_pro\19.3\quartus

# ../ex_25g/sim

# false

# false

# bit_32

# -t fs

# work work_lib altera_ver lpm_ver sgate_ver altera_mf_ver altera_lnsim_ver fourteennm_ver fourteennm_ct1_ver altera lpm sgate altera_mf altera_lnsim fourteennm fourteennm_ct1

# Model Technology ModelSim - Intel FPGA Edition vmap 10.5c Lib Mapping Utility 2017.01 Jan 23 2017

# vmap work ./libraries/work/

# Modifying modelsim.ini

# Model Technology ModelSim - Intel FPGA Edition vmap 10.5c Lib Mapping Utility 2017.01 Jan 23 2017

# vmap work_lib ./libraries/work/

# Modifying modelsim.ini

# altera_common_sv_packages 1 altera_xcvr_native_s10_htile_1921 1 alt_e25s10_1930 1 altera_xcvr_atx_pll_s10_htile_191 1 altera_xcvr_reset_control_s10_191 1 altera_merlin_master_translator_191 1 altera_merlin_slave_translator_191 1 altera_merlin_master_agent_191 1 altera_merlin_slave_agent_191 1 altera_avalon_sc_fifo_191 1 altera_merlin_router_191 1 altera_merlin_traffic_limiter_191 1 alt_hiconnect_sc_fifo_191 1 altera_merlin_burst_adapter_191 1 altera_merlin_demultiplexer_191 1 altera_merlin_multiplexer_191 1 altera_mm_interconnect_191 1 alt_e25s10_avmm_fabric_multichannel_1930 1 ex_25g 1

# altera_common_sv_packages altera_xcvr_native_s10_htile_1921 alt_e25s10_1930 altera_xcvr_atx_pll_s10_htile_191 altera_xcvr_reset_control_s10_191 altera_merlin_master_translator_191 altera_merlin_slave_translator_191 altera_merlin_master_agent_191 altera_merlin_slave_agent_191 altera_avalon_sc_fifo_191 altera_merlin_router_191 altera_merlin_traffic_limiter_191 alt_hiconnect_sc_fifo_191 altera_merlin_burst_adapter_191 altera_merlin_demultiplexer_191 altera_merlin_multiplexer_191 altera_mm_interconnect_191 alt_e25s10_avmm_fabric_multichannel_1930 ex_25g

# ** Error: couldn't create error file for command: permission denied

# Error in macro ./../ex_25g/sim/mentor/msim_setup.tcl line 233

# couldn't create error file for command: permission denied

# while executing

# "error [FixExecError $msg]"

# (procedure "vmap" line 29)

# invoked from within

# "vmap $library ./libraries/$library/"

# ("foreach" body line 3)

# invoked from within

# "foreach library $libraries {

# ensure_lib ./libraries/$library/

# vmap $library ./libraries/$library/

# lappend logical_libraries $library

# }"

-------------------------------------------------------------------------------------------------

The second method that I tried is to copy all the *.vhd,*.v,*.sv files in a seperate folder and compile them in modelsim in work library only (and of course changing the library in the internal files).

In this process, I face an error and mdoelsim exits with code 211 along with this info in vstf file:

# Current time Fri Apr 23 11:05:48 2021

# ModelSim - Intel FPGA Edition Stack Trace

# Program = vsim

# Id = "10.5c"

# Version = "2017.01"

# Date = "Jan 23 2017"

# Platform = win32pe

# Signature = 5e7f9b833961c34eb19f3225262e3a77

# 0 0x71046b2e: 'fdopen + 0x844' in 'c:\windows\system32\msvcr120.dll'

# 1 0x710b4aaf: 'vsnprintf_l + 0x81' in 'c:\windows\system32\msvcr120.dll'

# 2 0x710b4a29: 'vsnprintf + 0x16' in 'c:\windows\system32\msvcr120.dll'

# 3 0x01299c54: '<unknown (@0x1299c54)>'

# 4 0x004c13d2: '<unknown (@0x4c13d2)>'

# End of Stack Trace

Kindly help me.

Regards

Abhinav Behl

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

What Quartus version that you are using? Could you please double-check if there is any permission (write enable) concern on your system?

Regards -SK Lim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SengKok_L_Intel,

Thanks for your prompt reply,

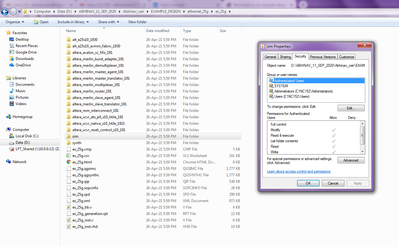

I am using Quartus 19.3. And yes I have double-checked write permissions, I am running it on windows and every permission is given to all files.

Yesterday I also tried one more thing to open the ModelSim GUI and add files manually and then compile using compile auto-generate option in ModelSim. In compilation also get errors. Apart from that when I try to run the simulation for top-level design, Modelsim exits with code 211 and the same message is printed in the .vstf file(to check vstf file I am told by ModelSim). For this step, I have attached the transcript file.

Please help me!

Regards

Abhinav Behl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

PS: sorry there was some mistakes in the compilation, even though I have solved all the compilation error I am still unable to simulate top-level design only (exiting with code 211). I am attaching the screenshot of the ModelSim window also.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems like you are not using a compatible version of Modelsim Sim.

I have done a quick test, the 25G IP simulation is working fine with the Modelsim

Sim Intel FPGA edition 2019.2 for Quartus v19.3.

Regards

-SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SengKok_L_Intel,

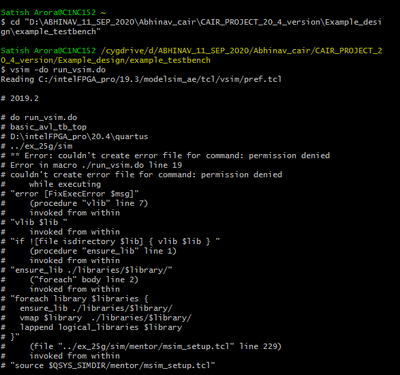

I am also using the modelsim intel FPGA 2019.2 for Quartus v19.3, I am running using Cygwin command window but getting following error:

I have no idea how you are able to run the simulation for the 25G IP, can you share the details. The steps I am following are:

1. generate the example design from Quartus

2. GOTO directory/<example_testbench>

3. run "vsim -do run_vsim.do" command from cmd prompt.

I am also attaching permission of sim directory at which ModelSim is throwing error

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SengKok_L_Intel,

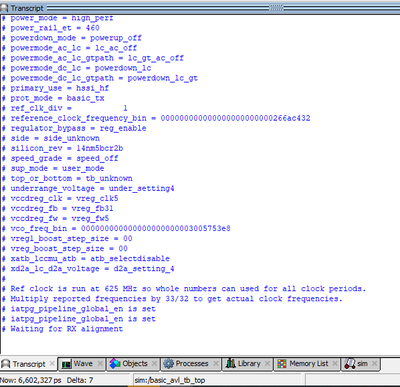

I was somehow managed to break the script into smaller scripts and was able to run the compilation, but after the compilation when I try to run the simulation I am still facing the error. I am attaching my transcript along in the attached section please review it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I was running at Linux by using v19.3 and using the same script as you, everything looks fine. Today, I tested it in my window system with v20.4 (v19.3 is not available in my setup), and it is working fine as well. Since v19.3 was an older version, I would suggest you move to v20.4 or later, and if you still encounter the problem, we can debug from there.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SengKok_L_Intel ,

As per your suggestion, I have Quartus 20.4 installed on my laptop. When I try to run the script from Cygwin I am getting the same issue. I am attaching the screenshot for it. I am using intel FPGA ModelSim version 2019.2

To remove these error I breakdown the script and compiled in ModelSim. I was able to run the "com" command (which is for compiling files in the correct order(as per the script)). But when I try to run the "elab" command I am getting the same error as with the previous versions. I am attaching the transcript for the same( after running "elab").

Let me know if you require any other files.

Kindly help me I am stuck with this problem for a very long.

Regards

Abhinav Behl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you please try this:

- Open the Modelsim

- Change the directory to example_testbench

- Go to tool -> TCL -> execute macro -> run_vsim.do

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

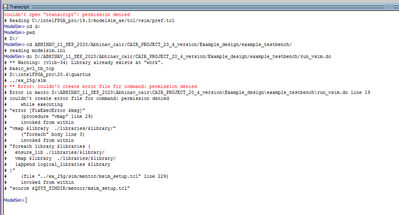

Hi @SengKok_L_Intel,

I tried the steps facing the error, attaching the screenshot.

Regards

Abhinav behl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The error message indicates there is a write access problem in your simulation folder. Perhaps you may try to run it in a different folder or another PC. From my window 10 PC, I did not encounter this problem, and this problem should not relate to the simulation script but your simulation directory writes permission.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SengKok_L_Intel,

I tried on some other PC the simulation was up, but the test case is still not passing. I tried running simulations for both MAC+PCS+PMA and MAC+PCS. In both the testcases, I am waiting for RX alignment. I have also attached the transcript for the MAC+PCS+PMA test case.

Kindly help!!

PS: In the IP generate section I have only selected mac statistics counters and simulation results are for single-channel design only.

Regards

Abhinav Behl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please let the simulation run for a longer time. It requires some time for Alignment Marker to lock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If further support is needed in this thread, please post a response within 15 days. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page