I am getting the following errors while programming the Stratix 10 GX board with the PCIE hard ip+ example design.

quartus_pro 19.4

Error (18950): Device has stopped receiving configuration data

Error (18948): Error message received from device: Detected hardware access error. There is a failure in accessing external hardware. (Subcode 0x0032, Info 0x00000000, Location 0x0000CC00)

Error (20072): A PMBUS error has occurred during configuration. Potential errors: Incorrect VID setting in Quartus Project. The target device fails to communicate to smart regulator or PMBUS Master on board.

Why am I getting these errors as all vid settings are auto generated? How to solve these issues?

链接已复制

Hi,

To better understanding the problem, could you please provide the following info?

- How do you generate the example design? Is this from the IP GUI?

- Did you connect the board to a proper setup, where there is PCIe reference clock coming to the FPGA end point?

Regards -SK

Hi @SengKok_L_Intel ,

I generated this example design using Quartus pro GUI. Specifically, I am following the steps present here

Thanks for the reply.

Did you connect the PCIe End point to the root port with the proper PCIe reference clock before you program the SOF? If without a proper PCIe reference clock, you will fail the programming.

Regards -SK

Hi @SengKok_L_Intel ,

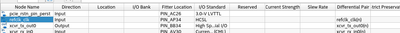

I did not find any such step in the manual so I have not specifically defined it, but shouldn't it be already done while generating the example design? Also does this attachment help or should I provide any other file? Sorry, I am not much familiar with this IP.

The refclk pin is connected to PIN_AK41

I am attaching the .qsf file for all the pin assignments and while generating the design I parameterized the port type as "native endpoint" and not "Root port".

Hi,

I believe you are using this development kit?

Do you actually slot this card into a host PC?

Regards -SK

Yes the device ID is 1SG280LN2F43E2VG and is placed in a server along with another exactly same card

Hi,

Are you using a custom board and this is not Intel FPGA development kit? I'm asking this is because, the device ID 1SG280LN2F43E2VG is not the same as Stratix 10 Development Kit at the link below:

Other questions:

- Does the server is power up, and there is a valid PCIe clock sending from the server to FPGA when you program the FPGA?

- Do you able to program a simple design (without the PCIe)?

Regards -SK

Hi @SengKok_L_Intel ,

It's actually BittWare's 520n card:

https://www.bittware.com/fpga/520n/

There is a valid PCIE clock being sent to the FPGA and I am able to program a simpler design without PCIE ip

I am attaching the qsf file of my simple design and I am also attaching the qsf of a vendor provided design which also has pcie instantiated

As i can see, you did not change the power and VID settings accordingly. Could you please give it a try of the attached qsf file?

Regards -SK

Hi @SengKok_L_Intel ,

The previous errors are gone but now I am getting this error:

Error (18950): Device has stopped receiving configuration data

Error (18948): Error message received from device: Device is in configuration state.

Error (209012): Operation failed

From the vendor.qsf file, the PCIe reference clock is using T34, but you are using AK41. Could you please double check? Or perhaps you can get a simple PCIe design from Bittware?

set_location_assignment PIN_T34 -to pcie_refclk

Regards -SK

Hi @SengKok_L_Intel ,

I changed the refclk pin to the same as the vendor one and also changed the rest of the pins according the vendor's pin configuration. But there is still an error while programming the board:

Error(18952): Error status: Device does not accept configuration request

Hi @SengKok_L_Intel ,It seems I need to get the server rebooted first. I will update you once I get it rebooted.

Thank for the update. If this still can't work, probably you can request a simple design from Bittware that can work properly for reference. This is to ensure all the pin assignments and VID setting are correct.

Regards -SK

If further support is needed in this thread, please post a response within 15 days. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.