- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In Partial Reconfiguration flow, I've noticed that when I compile

a Persona Implementation, it generates both the full bitstream(.sof) and

partial bitstreams for all PR partitions(.pmsf and .rbf).

I set the device as Agilex.

1. Is there an option not to generate .sof file for the Persona Implementation?

We will load the .sof file for the Base Implementation and program

the PR partitions with .rbf files. So, I think .sof file for the Persona Implementation

is unnecessary.

2. Is there an option to generate partial bitstream for specific PR partitions only?

In AMD(Xilinx) counterpart for example, they have an option(-cell option) to generate

partial bistream only.

(https://docs.xilinx.com/r/2021.1-English/ug835-vivado-tcl-commands/write_bitstream)

The command for the Quartus is "quartus_asm," and I wasn't able to find

any related option for quartus_asm command. I wonder if this is possible.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The .sof files for each implementation revision allow you to test your design with that persona in place without having to perform a PR first. If you don't use them, just ignore or trash them.

Once you have a .pmsf file for a partition, use Convert Programming Files to create a .rbf for it. Your workaround is saying that partition_2 is a SUPR (static update PR) region. Normally a .rbf file is created for a SUPR region even though you can't use that .rbf to PR a SUPR region during runtime (why it's call static). I guess I'm not sure what your goal is with (2).

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

2. is resolved by having

set_instance_assignment -name RBF_FILE_GENERATION_FOR_SUPR OFF -to pr_partition_2in .qsf file. I am not sure why the it is RBF_FILE_GENERATION_FOR_"SUPR", but it seems to exclude

pr_partition_2 when generating partial bitstreams.

Quartus is still generating the full bitstream(*.sof), so 1. is not resolved yet.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The .sof files for each implementation revision allow you to test your design with that persona in place without having to perform a PR first. If you don't use them, just ignore or trash them.

Once you have a .pmsf file for a partition, use Convert Programming Files to create a .rbf for it. Your workaround is saying that partition_2 is a SUPR (static update PR) region. Normally a .rbf file is created for a SUPR region even though you can't use that .rbf to PR a SUPR region during runtime (why it's call static). I guess I'm not sure what your goal is with (2).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the prompt reply.

The objective of (1) and (2) are both to reduce the bit generation time.

What I am trying to do with (1) is that

if I can generate only .rbf file for partition_1, for instance,

then the bit generation time is shorter than when I generate both .sof file and .rbf file for partition_1.

I wonder if there exists any option for this.

Regarding my workaround...

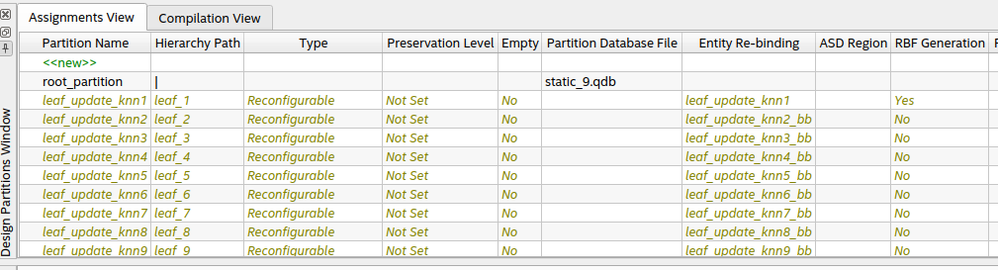

below is the Design Partitions Window, and I set the "RBF Generation" as "No" for leaf_2~leaf_9 so that I don't generate

.rbf files for them. They are NOT set as SUPR. I checked the SUPR tutorial in here(https://github.com/intel/fpga-partial-reconfig/tree/master/tutorials/agilex_pcie_devkit_blinking_led_supr), and

if they are set as SUPR partition, they are not colored yellow I guess.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does it take that long to generate the .sof? Compilation is long enough as it is. Generating programming files for me at least is the shortest part of the whole process.

If you really want to save that time, disable auto running of the Assembler during compilation and then run it manually when you do need the files.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No it doesn't take too long, but just a research/fun purpose.

I just want to know what granularity of commands Quartus provides.

Because you are here, just one more related question...

As I am using Agilex, it seems to generate .sof and .rbf with the compilation.

(I assume that there exists an option to NOT generate bitstream with compilation to make it separate runs.)

But for different devices like Arria 10 and Cyclone 10, it seems like

users can generate PR bitstreams with Converting Programming Files.

So, is .pmsf file the output of the Fitter?

Then, should a user generate .rbf file from .pmsf file with Converting Programming Files Dialog Box?

And it seems like .sof file is generated along the way of generating .rbf file and there's no way to prevent it for now?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Cyclone 10 doesn't support PR.

.pmsf is output specifically only when PR is enabled and set up. In Arria 10, if automatic .rbf file creation is disabled (which is an option; in Stratix 10 and perhaps Agilex, they are always created), then yes, you convert the .pmsf to .rbf manually with the CPF dialog.

.sof has always been created with the other files for testing, as I mentioned.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, I meant Cyclone 10 GX.

I am using Quartus Prime Pro 22.2 and according to the PR user guide,

(https://www.intel.com/content/www/us/en/docs/programmable/683834/22-2/faq.html)

.rbf file can be automatically generated for Arria 10 and Cyclone 10 GX with the commands below included in .qsf.

set_global_assignment -name GENERATE_PR_RBF_FILE ON

set_global_assignment -name ON_CHIP_BITSTREAM_DECOMPRESSION OFF

I am compiling Agilex device, and the Fitter doesn't seem to output .pmsf file.

quartus_asm command seems to output .pmsf along the way of generating .rbf file. Please correct me if I am wrong..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So .pmsf only generated for A10 and C10: https://www.intel.com/content/www/us/en/docs/programmable/683834/22-2/step-9-program-the-fpga-device.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi dj-park,

I hope the reply provided by sstrell above addressed your question. Do you still have further inquiries on this issue? Please feel free to let me know if there is any concern so that we could further assist you.

Otherwise, this thread will be idling and marked as inactive, thus it will be transitioned to community support because there is no update received from you in a while.

Regards,

Fakhrul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page