- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have managed to get it to work on breadboard with hardware so I'm guessing my logic is correct but i'm new to Quartus and could do with a few pointers to why I cannot get any output from my circuit, I have compiled the circuit and selected the file I wish to get my waveform from but I always get no output. Any pointers would be great help, thank you so much

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Don't do schematics. Implement in Verilog or VHDL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I notice that you are using the free edtion of the software version 8.1. Could you upgrade the design to the latest version? You may install the Lite editon (free edition) software from https://fpgasoftware.intel.com/19.1/?edition=lite&platform=windows

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

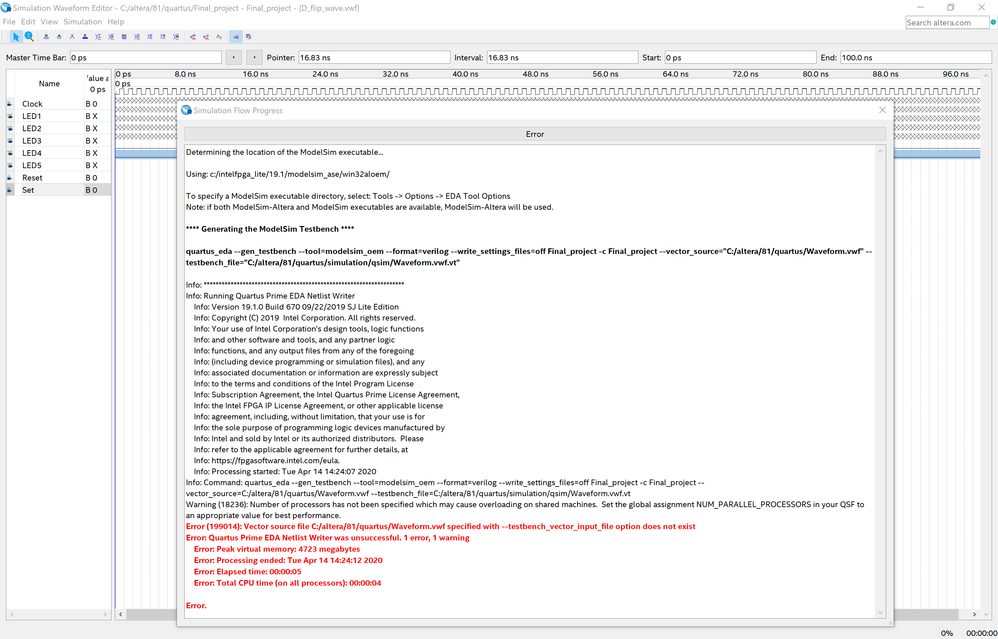

Hi Thank you for the advice and link, I have now downloaded and ran my circuit here however I'm still getting an error, any suggestions for this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You might also try toggling the reset in your testbench. You're holding it high so the registers never reset.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The error 199014 indicates that you specified a vector source file name using the --vector_source option, but the specified vector source file does not exist. Can you check whether you have this file in the path specified in the error message?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

From the scrren shot, I can see that the clock signal does not toggle.

Can you simulate using ModelSim Starter edition (Free edition)? You may

- Convert the BDF file to HDL file by clicking on File > Create/Update > Create HDL Design File From Current File

- Create Test Bench template by clicking on Processing > Start > Start Test Bench Template Write

- Find the test bench created in simulation/modelsim/*.vt or .vht, edit the test bench with the input signal

- Simulate the design

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

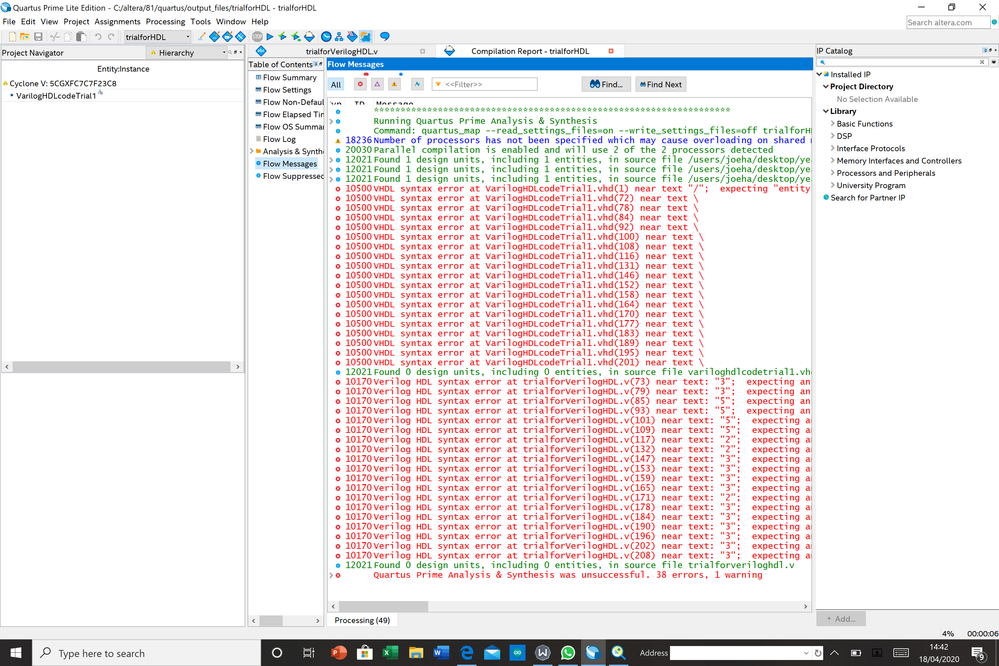

I have got a screen full of text now with the following code, now i'm very new to code and if i'mnot mistaken i need to change the quite a lot here becauseit looks nothing like what I expected and when i try to compile I get errors with expected "entity or "architecture" etc. so I have changed where I think it is appropriate however I am still getting the following flow errors, could you advise? thanks again, you've been great help so far. Below i have pasted what i get from what you instructed, is this correct? I'm struggling again, apologies

/ PROGRAM "Quartus Prime"

// VERSION "Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition"

// CREATED "Fri Apr 17 14:21:25 2020"

module D_flipflop( <Error (10500): VHDL syntax error at VarilogHDLcodeTrial1.vhd(5) > It asks for"is" then after that asks for "of"

Clock,

Set,

Reset,

LEDA,

LEDB,

LEDC,

LEDD,

LEDE

);

input wire Clock;

input wire Set;

input wire Reset;

output wire LEDA;

output wire LEDB;

output wire LEDC;

output wire LEDD;

output wire LEDE;

wire SYNTHESIZED_WIRE_76;

wire SYNTHESIZED_WIRE_77;

wire SYNTHESIZED_WIRE_78;

wire SYNTHESIZED_WIRE_79;

wire SYNTHESIZED_WIRE_80;

wire SYNTHESIZED_WIRE_81;

wire SYNTHESIZED_WIRE_82;

wire SYNTHESIZED_WIRE_83;

wire SYNTHESIZED_WIRE_84;

wire SYNTHESIZED_WIRE_20;

wire SYNTHESIZED_WIRE_21;

wire SYNTHESIZED_WIRE_22;

wire SYNTHESIZED_WIRE_23;

wire SYNTHESIZED_WIRE_85;

wire SYNTHESIZED_WIRE_54;

wire SYNTHESIZED_WIRE_55;

wire SYNTHESIZED_WIRE_56;

wire SYNTHESIZED_WIRE_57;

wire SYNTHESIZED_WIRE_58;

wire SYNTHESIZED_WIRE_59;

wire SYNTHESIZED_WIRE_60;

wire SYNTHESIZED_WIRE_61;

wire SYNTHESIZED_WIRE_62;

wire SYNTHESIZED_WIRE_63;

wire SYNTHESIZED_WIRE_64;

wire SYNTHESIZED_WIRE_65;

wire SYNTHESIZED_WIRE_66;

wire SYNTHESIZED_WIRE_67;

wire SYNTHESIZED_WIRE_68;

wire SYNTHESIZED_WIRE_69;

wire SYNTHESIZED_WIRE_70;

wire SYNTHESIZED_WIRE_71;

wire SYNTHESIZED_WIRE_72;

wire SYNTHESIZED_WIRE_73;

wire SYNTHESIZED_WIRE_74;

wire SYNTHESIZED_WIRE_75;

assign LEDA = SYNTHESIZED_WIRE_77;

assign LEDB = SYNTHESIZED_WIRE_79;

assign LEDC = SYNTHESIZED_WIRE_81;

assign LEDD = SYNTHESIZED_WIRE_83;

assign LEDE = SYNTHESIZED_WIRE_80;

\7408 b2v_inst(

.3(SYNTHESIZED_WIRE_76),

.2(SYNTHESIZED_WIRE_77),

.1(SYNTHESIZED_WIRE_57));

\7408 b2v_inst1(

.3(SYNTHESIZED_WIRE_78),

.2(SYNTHESIZED_WIRE_79),

.1(SYNTHESIZED_WIRE_59));

entity 7421 b2v_inst10( < Should I be inserting "entity" in here?

.5(SYNTHESIZED_WIRE_80),

.4(SYNTHESIZED_WIRE_81),

.3(SYNTHESIZED_WIRE_76),

.2(SYNTHESIZED_WIRE_82),

.1(SYNTHESIZED_WIRE_72));

\7421 b2v_inst11( < Should I be inserting "entity" in here?

.5(SYNTHESIZED_WIRE_83),

.4(SYNTHESIZED_WIRE_81),

.3(SYNTHESIZED_WIRE_76),

.2(SYNTHESIZED_WIRE_82),

.1(SYNTHESIZED_WIRE_67));

\7421 b2v_inst12(

.5(SYNTHESIZED_WIRE_84),

.4(SYNTHESIZED_WIRE_81),

.3(SYNTHESIZED_WIRE_79),

.2(SYNTHESIZED_WIRE_82),

.1(SYNTHESIZED_WIRE_56));

\7421 b2v_inst13(

.5(SYNTHESIZED_WIRE_80),

.4(SYNTHESIZED_WIRE_83),

.3(SYNTHESIZED_WIRE_81),

.2(SYNTHESIZED_WIRE_76),

.1(SYNTHESIZED_WIRE_58));

\7474 b2v_inst14(

.2D(SYNTHESIZED_WIRE_20),

.2PRN(Set),

.1CLK(Clock),

.1D(SYNTHESIZED_WIRE_21),

.1PRN(Set),

.2CLK(Clock),

.2CLRN(Reset),

.1CLRN(Reset),

.1QN(SYNTHESIZED_WIRE_82),

.2Q(SYNTHESIZED_WIRE_79),

.2QN(SYNTHESIZED_WIRE_76),

.1Q(SYNTHESIZED_WIRE_77));

\7474 b2v_inst15(

.2D(SYNTHESIZED_WIRE_22),

.2PRN(Set),

.1CLK(Clock),

.1D(SYNTHESIZED_WIRE_23),

.1PRN(Set),

.2CLK(Clock),

.2CLRN(Reset),

.1CLRN(Reset),

.1QN(SYNTHESIZED_WIRE_78),

.2Q(SYNTHESIZED_WIRE_83),

.2QN(SYNTHESIZED_WIRE_84),

.1Q(SYNTHESIZED_WIRE_81));

\7408 b2v_inst16(

.3(SYNTHESIZED_WIRE_84),

.2(SYNTHESIZED_WIRE_79),

.1(SYNTHESIZED_WIRE_60));

\7408 b2v_inst2(

.3(SYNTHESIZED_WIRE_78),

.2(SYNTHESIZED_WIRE_77),

.1(SYNTHESIZED_WIRE_55));

\7408 b2v_inst20(

.3(SYNTHESIZED_WIRE_84),

.2(SYNTHESIZED_WIRE_81),

.1(SYNTHESIZED_WIRE_63));

\7408 b2v_inst21(

.3(SYNTHESIZED_WIRE_78),

.2(SYNTHESIZED_WIRE_79),

.1(SYNTHESIZED_WIRE_62));

\7411 b2v_inst22(

.2(SYNTHESIZED_WIRE_78),

.3(SYNTHESIZED_WIRE_83),

.4(SYNTHESIZED_WIRE_80),

.1(SYNTHESIZED_WIRE_61));

\7408 b2v_inst27(

.3(SYNTHESIZED_WIRE_80),

.2(SYNTHESIZED_WIRE_84),

.1(SYNTHESIZED_WIRE_68));

\7408 b2v_inst28(

.3(SYNTHESIZED_WIRE_84),

.2(SYNTHESIZED_WIRE_77),

.1(SYNTHESIZED_WIRE_71));

\7408 b2v_inst29(

.3(SYNTHESIZED_WIRE_85),

.2(SYNTHESIZED_WIRE_83),

.1(SYNTHESIZED_WIRE_69));

\7408 b2v_inst30(

.3(SYNTHESIZED_WIRE_78),

.2(SYNTHESIZED_WIRE_77),

.1(SYNTHESIZED_WIRE_70));

\7408 b2v_inst34(

.3(SYNTHESIZED_WIRE_85),

.2(SYNTHESIZED_WIRE_83),

.1(SYNTHESIZED_WIRE_64));

\7408 b2v_inst35(

.3(SYNTHESIZED_WIRE_85),

.2(SYNTHESIZED_WIRE_76),

.1(SYNTHESIZED_WIRE_65));

\7411 b2v_inst36(

.2(SYNTHESIZED_WIRE_79),

.3(SYNTHESIZED_WIRE_81),

.4(SYNTHESIZED_WIRE_84),

.1(SYNTHESIZED_WIRE_66));

\7421 b2v_inst37(

.5(SYNTHESIZED_WIRE_83),

.4(SYNTHESIZED_WIRE_78),

.3(SYNTHESIZED_WIRE_79),

.2(SYNTHESIZED_WIRE_77),

.1(SYNTHESIZED_WIRE_74));

\7474 b2v_inst40(

.2PRN(Set),

.1CLK(Clock),

.1D(SYNTHESIZED_WIRE_54),

.1PRN(Set),

.1CLRN(Reset),

.1QN(SYNTHESIZED_WIRE_85),

.1Q(SYNTHESIZED_WIRE_80));

assign SYNTHESIZED_WIRE_21 = SYNTHESIZED_WIRE_55 | SYNTHESIZED_WIRE_56 | SYNTHESIZED_WIRE_57;

assign SYNTHESIZED_WIRE_20 = SYNTHESIZED_WIRE_58 | SYNTHESIZED_WIRE_59 | SYNTHESIZED_WIRE_60;

assign SYNTHESIZED_WIRE_23 = SYNTHESIZED_WIRE_61 | SYNTHESIZED_WIRE_62 | SYNTHESIZED_WIRE_63;

assign SYNTHESIZED_WIRE_75 = SYNTHESIZED_WIRE_64 | SYNTHESIZED_WIRE_65 | SYNTHESIZED_WIRE_66 | SYNTHESIZED_WIRE_67;

assign SYNTHESIZED_WIRE_73 = SYNTHESIZED_WIRE_68 | SYNTHESIZED_WIRE_69 | SYNTHESIZED_WIRE_70 | SYNTHESIZED_WIRE_71;

assign SYNTHESIZED_WIRE_22 = SYNTHESIZED_WIRE_72 | SYNTHESIZED_WIRE_73;

assign SYNTHESIZED_WIRE_54 = SYNTHESIZED_WIRE_74 | SYNTHESIZED_WIRE_75;

endmodule

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The code you've generated from the schematic is Verilog code but your errors are VHDL errors. The compiler is, for some reason, trying to compile this Verilog code as VHDL code.

Do not edit the code at all. It looks like your filename has a .vhd extension instead of .v. Change it to .v since this is Verilog code. Then follow the rest of Khai's instructions.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok so I changed it to .v but it still gives me errors?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you provide the design.qar and the bdf file for investigation? To generate the QAR file, click on Project > Archive Project > Archive

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you zip the BDF file?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please see attached zip file. Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joseph,

In JK_flipflop.bdf, the logic gates on the left are overlapping to each other. You have to rearrage the gate so that they are not overlapping.

Warning (275011): Block or symbol "AND3" of instance "inst26" overlaps another block or symbol

Warning (275011): Block or symbol "AND3" of instance "inst28" overlaps another block or symbol

Warning (275011): Block or symbol "AND2" of instance "inst30" overlaps another block or symbol

Warning (275011): Block or symbol "OR2" of instance "inst32" overlaps another block or symbol

Warning (275011): Block or symbol "AND3" of instance "inst34" overlaps another block or symbol

Warning (275011): Block or symbol "AND3" of instance "inst37" overlaps another block or symbol

Warning (275011): Block or symbol "AND2" of instance "inst39" overlaps another block or symbol

Warning (275011): Block or symbol "AND3" of instance "inst42" overlaps another block or symbol

Besides this, I notice that you are instantiating the symbol from Others>maxplus2 which is for another legacy software, Max + PLus II. You have to recreate the design using megafunctions or primitives only. Please note that ModelSim-Intel FPGA edition does not support BDF file for simulation. You may convert the BDF file (after fixing the above error) with the steps provided in my previous reply and simulate using test bench but I would suggest you to design using HDL.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if you have any updates?

Thanks.

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page