- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all ,

I am using Quartus Prime ver 16.0 for compilation of my vhdl project files , the project compiles fine without any errors , but when i start simulation the Modelsim cantt seem to find my package file .

Modelsim version : ModelSim ALTERA STARTER EDITION 10.4d

Although i made a "work" folder myself and pasted the vhdl package in it , but still no effect , then i copied the folder and pasted it in D:\Quartus_projects\i2c_audio_Fir_filtr1p1\simulation\modelsim

Still i get this error :

# vcom -93 -work work {D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd}

# Model Technology ModelSim ALTERA vcom 10.4d Compiler 2015.12 Dec 30 2015

# Start time: 15:50:44 on Mar 07,2022

# vcom -reportprogress 300 -93 -work work D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd

# -- Loading package STANDARD

# -- Loading package TEXTIO

# -- Loading package std_logic_1164

# -- Loading package std_logic_arith

# -- Loading package STD_LOGIC_UNSIGNED

# -- Loading package NUMERIC_STD

# ** Error: (vcom-11) Could not find work.audio_codeci2c_pkg.

#

# ** Error (suppressible): D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd(11): (vcom-1195) Cannot find expanded name "work.audio_codeci2c_pkg".

#

# ** Error: D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd(11): Unknown expanded name.

# ** Error: D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd(13): VHDL Compiler exiting

# End time: 15:50:44 on Mar 07,2022, Elapsed time: 0:00:00

# Errors: 4, Warnings: 0

# ** Error: C:/altera_lite/16.0/modelsim_ase/win32aloem/vcom failed.

# Error in macro ./Audio_FIR_filter_run_msim_rtl_vhdl.do line 74

# C:/altera_lite/16.0/modelsim_ase/win32aloem/vcom failed.

# while executing

# "vcom -93 -work work {D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd}"

In my Top vhdl file and in my testbench i have declared it like this :

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- USE IEEE.std_logic_arith.ALL;

USE ieee.std_logic_unsigned.all;

USE ieee.numeric_std.ALL;

use ieee.math_real.all;

USE std.textio.ALL;

Library work;

use work.audio_codec_i2c_pkg.all;

Any clue why modelsim is not able to open it ???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Spelling difference? audio_codec_i2c_pkg vs. audio_codeci2c_pkg

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

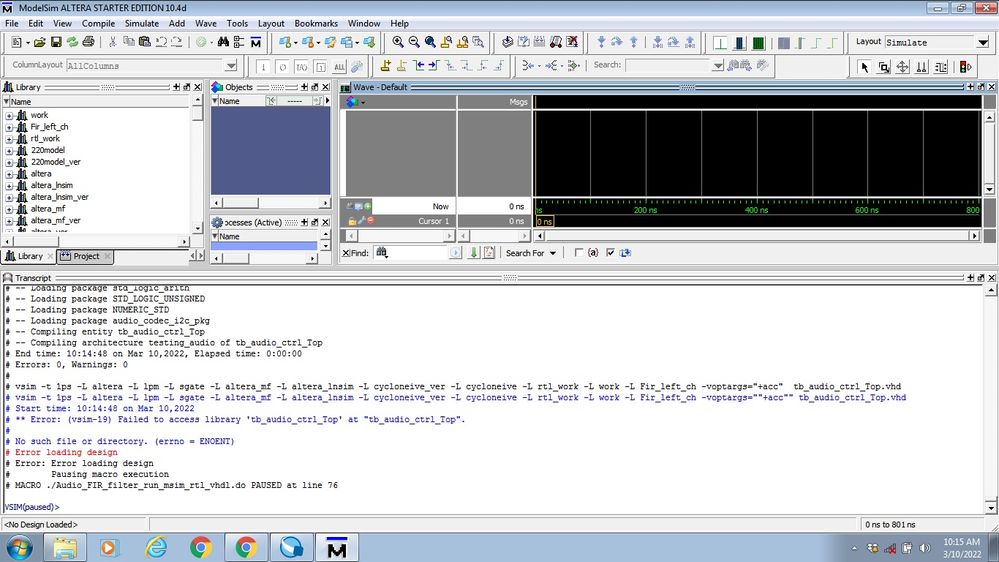

Thanks i got rid of that error , but now i am getting this error :

-- Loading package std_logic_arith

# -- Loading package STD_LOGIC_UNSIGNED

# -- Loading package NUMERIC_STD

# -- Loading package audio_codec_i2c_pkg

# -- Compiling entity tb_audio_ctrl_Top

# -- Compiling architecture testing_audio of tb_audio_ctrl_Top

# ** Warning: D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd(54): (vcom-1207) An abstract literal and an identifier must have a separator between them.

# ** Warning: D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd(54): (vcom-1207) An abstract literal and an identifier must have a separator between them.

# ** Warning: D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd(55): (vcom-1207) An abstract literal and an identifier must have a separator between them.

# ** Warning: D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd(55): (vcom-1207) An abstract literal and an identifier must have a separator between them.

# ** Warning: D:/Quartus_projects/i2c_audio_Fir_filtr1p1/source/tb_audio_ctrl_Top.vhd(58): (vcom-1207) An abstract literal and an identifier must have a separator between them.

# End time: 14:35:41 on Mar 08,2022, Elapsed time: 0:00:00

# Errors: 0, Warnings: 5

#

# vsim -t 1ps -L altera -L lpm -L sgate -L altera_mf -L altera_lnsim -L cycloneive_ver -L cycloneive -L rtl_work -L work -L Fir_left_ch -voptargs="+acc" tb_audio_ctrl_Top.vhd

# vsim -t 1ps -L altera -L lpm -L sgate -L altera_mf -L altera_lnsim -L cycloneive_ver -L cycloneive -L rtl_work -L work -L Fir_left_ch -voptargs=""+acc"" tb_audio_ctrl_Top.vhd

# Start time: 14:35:41 on Mar 08,2022

# ** Error: (vsim-19) Failed to access library 'tb_audio_ctrl_Top' at "tb_audio_ctrl_Top".

#

# No such file or directory. (errno = ENOENT)

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./Audio_FIR_filter_run_msim_rtl_vhdl.do PAUSED at line 76

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you show the code lines from the file that are mentioned as having issues?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have generated some IPs in Quartus Prime Pro edition software and due to some reason I am trying to simulate the design in Modelsim -INTEL FPGA Starter edition and I am facing errors like this:

** Error: (vsim-3033) ../.../IP_Folder/pll_div_by2/altera_iopll_1931/sim/stratix10_altera_iopll.v(498): Instantiation of 'fourteennm_iopll' failed. The design unit was not found.

** Error (suppressible): (vsim-19) Failed to access library 'fourteennm_ver' at "fourteennm_ver".

# No such file or directory. (errno = ENOENT).

so can someone please help me? what is my mistake and how to solve this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Testbench :

-- Testbench for the i2c_audio_ctrl_Top.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.all;

USE ieee.numeric_std.ALL;

USE IEEE.std_logic_arith.ALL;

Library work;

USE work.audio_codec_i2c_pkg.All;

ENTITY tb_audio_ctrl_Top IS

END tb_audio_ctrl_Top;

ARCHITECTURE testing_audio OF tb_audio_ctrl_Top IS

COMPONENT i2c_audio_ctrl_Top

port (

CLOCK_50 : in std_logic;

PUSHB : in std_logic_vector ( 3 downto 0 );

LED : out std_logic_vector ( 3 downto 0 );

SW : in std_logic_vector ( 17 downto 0 );

LEDR : out std_logic_vector ( 17 downto 0 );

LEDG : out std_logic_vector ( 7 downto 0 );

GPIO : out std_logic_vector ( 35 downto 0 ); -- 40-pin Connector

I2C_SCLK : out std_logic;

I2C_SDAT : inout std_logic;

--audio codec ports

AUD_ADCDAT : in std_logic;

AUD_ADCLRCK: out std_logic;

AUD_DACLRCK: out std_logic;

AUD_DACDAT : out std_logic;

AUD_XCK : out std_logic;

AUD_BCLK : out std_logic

);

END COMPONENT;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm guessing the simulator doesn't like your use of "us" and "ms" right after a value without a space.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks again for pointing that out , i did get rid of those warnings , but i still get that error :

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

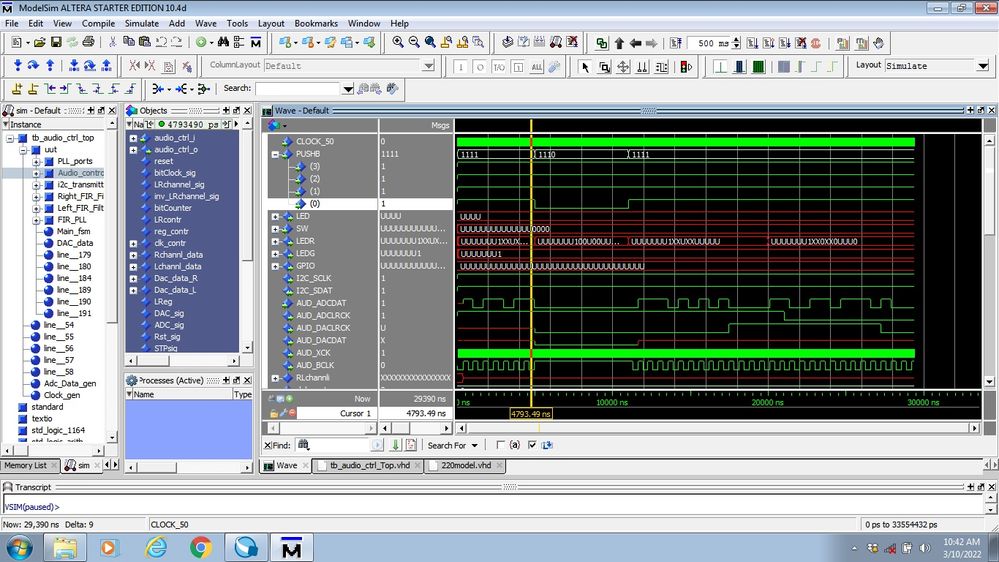

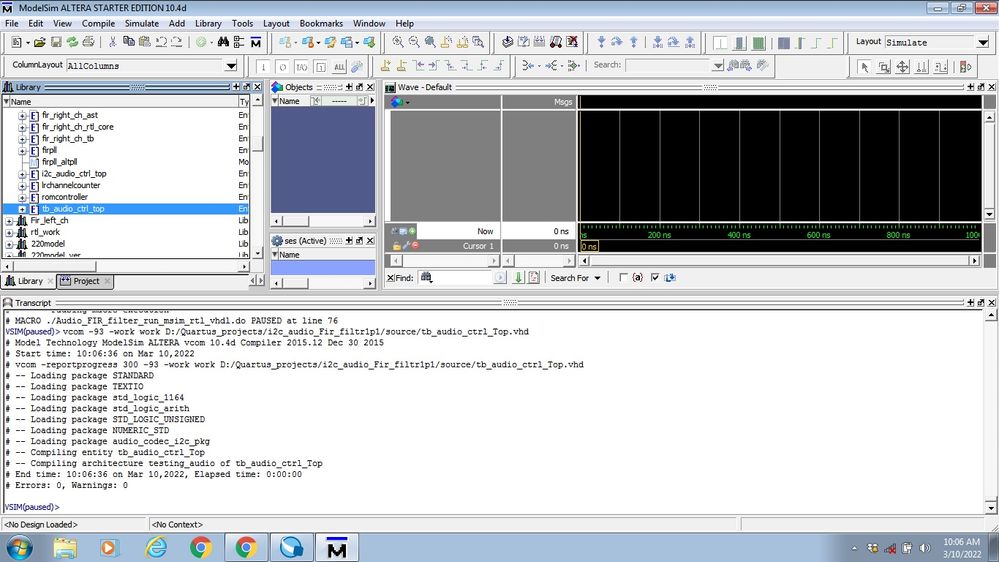

With in Modelsim in the above attached pic , i noticed that Modelsim only has "Fir_left_ch" , although in vhdl top file i have two Fir ip included one for left and other for right channel . Anyway i right clicked on the tb in the work folder and forced compiled it , and it successfully compiled it and then simulated the tb and it worked .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I still want to get rid of this annoying error which pops up when i start simulating from Quartus i.e "# ** Error: (vsim-19) Failed to access library 'tb_audio_ctrl_Top' at "tb_audio_ctrl_Top".

Why do i have to force compile and simulate the tb

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ahmed,

You probably need to look at below KDB related to your issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ahmed,

Let me know if there is any update or concern on this

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is output of verror 19 :

vsim -t 1ps -L altera -L lpm -L sgate -L altera_mf -L altera_lnsim -L cycloneive_ver -L cycloneive -L rtl_work -L work -L Fir_left_ch -voptargs="+acc" tb_audio_ctrl_Top.vhd

# vsim -t 1ps -L altera -L lpm -L sgate -L altera_mf -L altera_lnsim -L cycloneive_ver -L cycloneive -L rtl_work -L work -L Fir_left_ch -voptargs=""+acc"" tb_audio_ctrl_Top.vhd

# Start time: 19:01:11 on Mar 16,2022

# ** Error: (vsim-19) Failed to access library 'tb_audio_ctrl_Top' at "tb_audio_ctrl_Top".

#

# No such file or directory. (errno = ENOENT)

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./Audio_FIR_filter_run_msim_rtl_vhdl.do PAUSED at line 76

verror 19

#

# common Message # 19:

# The specified library could not be accessed at the specified location.

#

# Verify that the directories in the path exist and have the proper access

#

# permissions and that the "_info" file (with proper access permissions)

#

# exists. This message might be preceded or followed by another message

#

# that gives more information about the problem.

#

#

#

# The vlib command creates a ModelSim library. The vmap command creates

#

# the map from a logical library name to the physical library (directory).

#

# Use the vmap command without arguments to find out how all the libraries

#

# are mapped. In the absence of a mapping, the library is searched for in

#

# the current working directory.

#

#

#

# One way this problem can occur is if the mapping for the library in your

#

# modelsim.ini file contains an environment variable that is not set

#

# in your environment.

#

#

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And this is my modelsim.ini file :

; Copyright 1991-2009 Mentor Graphics Corporation

;

; All Rights Reserved.

;

; THIS WORK CONTAINS TRADE SECRET AND PROPRIETARY INFORMATION WHICH IS THE PROPERTY OF

; MENTOR GRAPHICS CORPORATION OR ITS LICENSORS AND IS SUBJECT TO LICENSE TERMS.

;

[Library]

others = $MODEL_TECH/../modelsim.ini

; Altera Primitive libraries

;

; VHDL Section

;

;

; Verilog Section

;

work = rtl_work

Fir_left_ch = Fir_left_ch

[vcom]

; VHDL93 variable selects language version as the default.

; Default is VHDL-2002.

; Value of 0 or 1987 for VHDL-1987.

; Value of 1 or 1993 for VHDL-1993.

; Default or value of 2 or 2002 for VHDL-2002.

; Default or value of 3 or 2008 for VHDL-2008.

VHDL93 = 2002

; Show source line containing error. Default is off.

; Show_source = 1

; Turn off unbound-component warnings. Default is on.

; Show_Warning1 = 0

; Turn off process-without-a-wait-statement warnings. Default is on.

; Show_Warning2 = 0

; Turn off null-range warnings. Default is on.

; Show_Warning3 = 0

; Turn off no-space-in-time-literal warnings. Default is on.

; Show_Warning4 = 0

; Turn off multiple-drivers-on-unresolved-signal warnings. Default is on.

; Show_Warning5 = 0

; Turn off optimization for IEEE std_logic_1164 package. Default is on.

; Optimize_1164 = 0

; Turn on resolving of ambiguous function overloading in favor of the

; "explicit" function declaration (not the one automatically created by

; the compiler for each type declaration). Default is off.

; The .ini file has Explicit enabled so that std_logic_signed/unsigned

; will match the behavior of synthesis tools.

Explicit = 1

; Turn off acceleration of the VITAL packages. Default is to accelerate.

; NoVital = 1

; Turn off VITAL compliance checking. Default is checking on.

; NoVitalCheck = 1

; Ignore VITAL compliance checking errors. Default is to not ignore.

; IgnoreVitalErrors = 1

; Turn off VITAL compliance checking warnings. Default is to show warnings.

; Show_VitalChecksWarnings = 0

; Keep silent about case statement static warnings.

; Default is to give a warning.

; NoCaseStaticError = 1

; Keep silent about warnings caused by aggregates that are not locally static.

; Default is to give a warning.

; NoOthersStaticError = 1

; Turn off inclusion of debugging info within design units.

; Default is to include debugging info.

; NoDebug = 1

; Turn off "Loading..." messages. Default is messages on.

; Quiet = 1

; Turn on some limited synthesis rule compliance checking. Checks only:

; -- signals used (read) by a process must be in the sensitivity list

; CheckSynthesis = 1

; Activate optimizations on expressions that do not involve signals,

; waits, or function/procedure/task invocations. Default is off.

; ScalarOpts = 1

; Require the user to specify a configuration for all bindings,

; and do not generate a compile time default binding for the

; component. This will result in an elaboration error of

; 'component not bound' if the user fails to do so. Avoids the rare

; issue of a false dependency upon the unused default binding.

; RequireConfigForAllDefaultBinding = 1

; Inhibit range checking on subscripts of arrays. Range checking on

; scalars defined with subtypes is inhibited by default.

; NoIndexCheck = 1

; Inhibit range checks on all (implicit and explicit) assignments to

; scalar objects defined with subtypes.

; NoRangeCheck = 1

[vlog]

; Turn off inclusion of debugging info within design units.

; Default is to include debugging info.

; NoDebug = 1

; Turn off "loading..." messages. Default is messages on.

; Quiet = 1

; Turn on Verilog hazard checking (order-dependent accessing of global vars).

; Default is off.

; Hazard = 1

; Turn on converting regular Verilog identifiers to uppercase. Allows case

; insensitivity for module names. Default is no conversion.

; UpCase = 1

; Turn on incremental compilation of modules. Default is off.

; Incremental = 1

; Turns on lint-style checking.

; Show_Lint = 1

[vsim]

; Simulator resolution

; Set to fs, ps, ns, us, ms, or sec with optional prefix of 1, 10, or 100.

Resolution = ps

; User time unit for run commands

; Set to default, fs, ps, ns, us, ms, or sec. The default is to use the

; unit specified for Resolution. For example, if Resolution is 100ps,

; then UserTimeUnit defaults to ps.

; Should generally be set to default.

UserTimeUnit = default

; Default run length

RunLength = 100

; Maximum iterations that can be run without advancing simulation time

IterationLimit = 5000

; Directive to license manager:

; vhdl Immediately reserve a VHDL license

; vlog Immediately reserve a Verilog license

; plus Immediately reserve a VHDL and Verilog license

; nomgc Do not look for Mentor Graphics Licenses

; nomti Do not look for Model Technology Licenses

; noqueue Do not wait in the license queue when a license isn't available

; viewsim Try for viewer license but accept simulator license(s) instead

; of queuing for viewer license

; License = plus

; Stop the simulator after a VHDL/Verilog assertion message

; 0 = Note 1 = Warning 2 = Error 3 = Failure 4 = Fatal

BreakOnAssertion = 3

; Assertion Message Format

; %S - Severity Level

; %R - Report Message

; %T - Time of assertion

; %D - Delta

; %I - Instance or Region pathname (if available)

; %% - print '%' character

; AssertionFormat = "** %S: %R\n Time: %T Iteration: %D%I\n"

; Assertion File - alternate file for storing VHDL/Verilog assertion messages

; AssertFile = assert.log

; Default radix for all windows and commands...

; Set to symbolic, ascii, binary, octal, decimal, hex, unsigned

DefaultRadix = symbolic

; VSIM Startup command

; Startup = do startup.do

; File for saving command transcript

TranscriptFile = transcript

; File for saving command history

; CommandHistory = cmdhist.log

; Specify whether paths in simulator commands should be described

; in VHDL or Verilog format.

; For VHDL, PathSeparator = /

; For Verilog, PathSeparator = .

; Must not be the same character as DatasetSeparator.

PathSeparator = /

; Specify the dataset separator for fully rooted contexts.

; The default is ':'. For example, sim:/top

; Must not be the same character as PathSeparator.

DatasetSeparator = :

; Disable VHDL assertion messages

; IgnoreNote = 1

; IgnoreWarning = 1

; IgnoreError = 1

; IgnoreFailure = 1

; Default force kind. May be freeze, drive, deposit, or default

; or in other terms, fixed, wired, or charged.

; A value of "default" will use the signal kind to determine the

; force kind, drive for resolved signals, freeze for unresolved signals

; DefaultForceKind = freeze

; If zero, open files when elaborated; otherwise, open files on

; first read or write. Default is 0.

; DelayFileOpen = 1

; Control VHDL files opened for write.

; 0 = Buffered, 1 = Unbuffered

UnbufferedOutput = 0

; Control the number of VHDL files open concurrently.

; This number should always be less than the current ulimit

; setting for max file descriptors.

; 0 = unlimited

ConcurrentFileLimit = 40

; Control the number of hierarchical regions displayed as

; part of a signal name shown in the Wave window.

; A value of zero tells VSIM to display the full name.

; The default is 0.

; WaveSignalNameWidth = 0

; Turn off warnings from the std_logic_arith, std_logic_unsigned

; and std_logic_signed packages.

; StdArithNoWarnings = 1

; Turn off warnings from the IEEE numeric_std and numeric_bit packages.

; NumericStdNoWarnings = 1

; Control the format of the (VHDL) FOR generate statement label

; for each iteration. Do not quote it.

; The format string here must contain the conversion codes %s and %d,

; in that order, and no other conversion codes. The %s represents

; the generate_label; the %d represents the generate parameter value

; at a particular generate iteration (this is the position number if

; the generate parameter is of an enumeration type). Embedded whitespace

; is allowed (but discouraged); leading and trailing whitespace is ignored.

; Application of the format must result in a unique scope name over all

; such names in the design so that name lookup can function properly.

; GenerateFormat = %s__%d

; Specify whether checkpoint files should be compressed.

; The default is 1 (compressed).

; CheckpointCompressMode = 0

; List of dynamically loaded objects for Verilog PLI applications

; Veriuser = veriuser.sl

; Specify default options for the restart command. Options can be one

; or more of: -force -nobreakpoint -nolist -nolog -nowave

; DefaultRestartOptions = -force

; HP-UX 10.20 ONLY - Enable memory locking to speed up large designs

; (> 500 megabyte memory footprint). Default is disabled.

; Specify number of megabytes to lock.

; LockedMemory = 1000

; Turn on (1) or off (0) WLF file compression.

; The default is 1 (compress WLF file).

; WLFCompress = 0

; Specify whether to save all design hierarchy (1) in the WLF file

; or only regions containing logged signals (0).

; The default is 0 (save only regions with logged signals).

; WLFSaveAllRegions = 1

; WLF file time limit. Limit WLF file by time, as closely as possible,

; to the specified amount of simulation time. When the limit is exceeded

; the earliest times get truncated from the file.

; If both time and size limits are specified the most restrictive is used.

; UserTimeUnits are used if time units are not specified.

; The default is 0 (no limit). Example: WLFTimeLimit = {100 ms}

; WLFTimeLimit = 0

; WLF file size limit. Limit WLF file size, as closely as possible,

; to the specified number of megabytes. If both time and size limits

; are specified then the most restrictive is used.

; The default is 0 (no limit).

; WLFSizeLimit = 1000

; Specify whether or not a WLF file should be deleted when the

; simulation ends. A value of 1 will cause the WLF file to be deleted.

; The default is 0 (do not delete WLF file when simulation ends).

; WLFDeleteOnQuit = 1

; Automatic SDF compilation

; Disables automatic compilation of SDF files in flows that support it.

; Default is on, uncomment to turn off.

; NoAutoSDFCompile = 1

[lmc]

[msg_system]

; Change a message severity or suppress a message.

; The format is: <msg directive> = <msg number>[,<msg number>...]

; Examples:

; note = 3009

; warning = 3033

; error = 3010,3016

; fatal = 3016,3033

; suppress = 3009,3016,3043

; The command verror <msg number> can be used to get the complete

; description of a message.

; Control transcripting of elaboration/runtime messages.

; The default is to have messages appear in the transcript and

; recorded in the wlf file (messages that are recorded in the

; wlf file can be viewed in the MsgViewer). The other settings

; are to send messages only to the transcript or only to the

; wlf file. The valid values are

; both {default}

; tran {transcript only}

; wlf {wlf file only}

; msgmode = both

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ahmed,

Are you managed to work on this issue? Is the KDB applicable at your end?

Let me know any update.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI ,

I havent been able to resolve this issue the "verror 19" refers to "modeslim.ini" file , but this file is generated by Modelsim-altera , and dont see any variable that is uncorrectly set in it ???

What is KDB ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is Modelsim-Atera output after i run "vmap"

vmap

# Reading modelsim.ini

# "work" maps to directory ./rtl_work.

# "Fir_left_ch" maps to directory ./Fir_left_ch.

# Reading C:/altera_lite/16.0/modelsim_ase/win32aloem/../modelsim.ini

# "std" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../std.

# "ieee" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../ieee.

# "verilog" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../verilog.

# "vital2000" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../vital2000.

# "std_developerskit" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../std_developerskit.

# "synopsys" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../synopsys.

# "modelsim_lib" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../modelsim_lib.

# "sv_std" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../sv_std.

# "altera_mf" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/altera_mf.

# "altera" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/altera.

# "altera_lnsim" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/altera_lnsim.

# "lpm" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/220model.

# "220model" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/220model.

# "maxii" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/maxii.

# "maxv" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/maxv.

# "fiftyfivenm" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/fiftyfivenm.

# "sgate" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/sgate.

# "arriaii" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/arriaii.

# "arriaii_hssi" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/arriaii_hssi.

# "arriaii_pcie_hip" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/arriaii_pcie_hip.

# "arriaiigz" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/arriaiigz.

# "arriaiigz_hssi" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/arriaiigz_hssi.

# "arriaiigz_pcie_hip" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/arriaiigz_pcie_hip.

# "stratixiv" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/stratixiv.

# "stratixiv_hssi" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/stratixiv_hssi.

# "stratixiv_pcie_hip" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/stratixiv_pcie_hip.

# "cycloneiv" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/cycloneiv.

# "cycloneiv_hssi" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/cycloneiv_hssi.

# "cycloneiv_pcie_hip" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/cycloneiv_pcie_hip.

# "cycloneive" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/cycloneive.

# "stratixv" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/stratixv.

# "stratixv_hssi" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/stratixv_hssi.

# "stratixv_pcie_hip" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/stratixv_pcie_hip.

# "arriavgz" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/arriavgz.

# "arriavgz_hssi" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/arriavgz_hssi.

# "arriavgz_pcie_hip" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/arriavgz_pcie_hip.

# "arriav" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/arriav.

# "cyclonev" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/cyclonev.

# "twentynm" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/twentynm.

# "twentynm_hssi" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/twentynm_hssi.

# "twentynm_hip" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/twentynm_hip.

# "fourteennm" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/vhdl/fourteennm.

# "altera_mf_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/altera_mf.

# "altera_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/altera.

# "altera_lnsim_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/altera_lnsim.

# "lpm_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/220model.

# "220model_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/220model.

# "maxii_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/maxii.

# "maxv_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/maxv.

# "fiftyfivenm_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/fiftyfivenm.

# "sgate_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/sgate.

# "arriaii_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriaii.

# "arriaii_hssi_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriaii_hssi.

# "arriaii_pcie_hip_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriaii_pcie_hip.

# "arriaiigz_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriaiigz.

# "arriaiigz_hssi_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriaiigz_hssi.

# "arriaiigz_pcie_hip_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriaiigz_pcie_hip.

# "stratixiv_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/stratixiv.

# "stratixiv_hssi_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/stratixiv_hssi.

# "stratixiv_pcie_hip_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/stratixiv_pcie_hip.

# "stratixv_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/stratixv.

# "stratixv_hssi_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/stratixv_hssi.

# "stratixv_pcie_hip_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/stratixv_pcie_hip.

# "arriavgz_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriavgz.

# "arriavgz_hssi_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriavgz_hssi.

# "arriavgz_pcie_hip_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriavgz_pcie_hip.

# "arriav_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriav.

# "arriav_hssi_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriav_hssi.

# "arriav_pcie_hip_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/arriav_pcie_hip.

# "cyclonev_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/cyclonev.

# "cyclonev_hssi_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/cyclonev_hssi.

# "cyclonev_pcie_hip_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/cyclonev_pcie_hip.

# "cycloneiv_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/cycloneiv.

# "cycloneiv_hssi_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/cycloneiv_hssi.

# "cycloneiv_pcie_hip_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/cycloneiv_pcie_hip.

# "cycloneive_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/cycloneive.

# "twentynm_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/twentynm.

# "twentynm_hssi_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/twentynm_hssi.

# "twentynm_hip_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/twentynm_hip.

# "fourteennm_ver" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../altera/verilog/fourteennm.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is vmap output of a working testbench another project :

# vmap

# Reading modelsim.ini

# "work" maps to directory ./rtl_work.

# Reading C:/altera_lite/16.0/modelsim_ase/win32aloem/../modelsim.ini

# "std" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../std.

# "ieee" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../ieee.

# "verilog" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../verilog.

# "vital2000" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../vital2000.

# "std_developerskit" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../std_developerskit.

# "synopsys" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../synopsys.

# "modelsim_lib" maps to directory C:/altera_lite/16.0/modelsim_ase/win32aloem/../modelsim_lib.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ahmed,

What is KDB ?

The Intel® FPGA Knowledge Base page provides links to applicable articles that span a variety of FPGA related issues. You may refer to link below for more KDB

You probably need to reinstall Modelsim and see if it can detect vhdl package for you simulation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

I dont think reinstalling Modelsim can solve the issue , as it is working fine for other projects , the mapping to libraries is perfect .

This modelsim.ini file has be generated again .

Regards ,

Ahmed

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page