- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This happens regularly :

In a design with working signaltap probes.

I add or remove a few signals and recompile.

After a full build I start up signaltap and it reports :

Start Rapid Recompile to continue.

The only way I have been able to recover is by removing ALL generated files from the database and rebuild.

Even that doesnt always work.

What does signaltap look for to decide that a recompile is necesary?

What is going on.

This is costing me several days each month.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If you've already done a full compile, you shouldn't have to do what you're doing. Even if it says to start a rapid recompile, have you tried connecting to and programming your device, using the .stp file as is? Is the option to use the .stp file enabled in the project settings (Assignments menu -> Settings)?

If you want to avoid accidentally making changes that require recompilation, turn on one of the lock modes in the .stp file window.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I always do a full compile.

Locking the changes is not relevant since signaltap indicates that a recompile is requires as soon as signaltap loads.

When I load the design with signaltap the new signals are visible in the signal list.

I have closed signaltap and quartus.

I have deleted the db and incremental_db directories.

I have deleted all directories generated by qsys.

I have checked out the source files from git and rebuild from scratch.

Nothing works.

Quartus/Signaltap is checking something to make this decision.

What is it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Rapid recompile usually take in if there are changes in the source code or changes on the stp files.

Can you try to just make a simple compile and look for if there are any code changes in the message in the synthesis?

What you can also do is create a simple design and make a signal tap run. Compare the message result in the working one and the non working one.

Let me know if this helps?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I ALWAYS do a full compile, NEVER rapid compile, see previous response.

This state remains the same if I dont touch ANYTHING :

- I start signaltap.

- Signaltap indicates a recompile is required.

- I close signaltap

- I run a full compile

- I start signaltap

- Signaltap indicates a recompile is required.

- I close signaltap

- I run a full compile

- I start signaltap

- Signaltap indicates a recompile is required.

- I close signaltap

- I run a full compile

- I start signaltap

etc...

If there was a change in the source files the recompile would have taken care of that.

I think there is a file that Quartus generates that is in a bad state.

Quartus/Signaltap is checking something to make this decision.

What is it?

If you are an expert on this tool you should be able to answer that question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Again, have you tried running the logic analyzer even if the status says you need to recompile?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

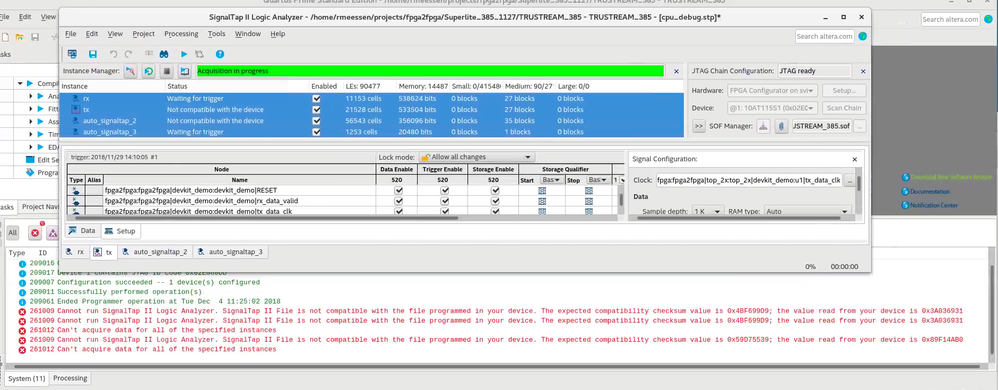

Yes I have:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hmm. You have multiple instances. If you disable the instances that it says are not compatible, does it work?

There might be something in those particular instances that is causing the issue. Perhaps you're trying to tap post-fit nodes that no longer exist after some change you made a while ago. Check those instances to see if you have any red signals in the node list. If the tapped nodes can't be found by Signal Tap, it will indicate you need to recompile to connect to them. But if they don't exist, it still won't work. This could be the problem.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page