How to get clock name on which the register is running in Q std?solved only using get_path, but during synthesis I get an error because get_path is not from sdc or sdc_ext package

链接已复制

where do you plan to put this get_register? Are you planning to put it in *.sdc? If yes, you may have to run timing analyzer to get the correct nodes.

To find the correct nodes, what you can do is go to Timing analyzer -> Constrain -> set_multiclycle_path -> select the nodes that you want.

set_clock_groups -physically_exclusive -group [get_clocks {clk}] -group [get_clocks {vidi_clock}]

however, in the toplevel file, these clocks are named differently. And I would like to use this module in other projects. That is, create an IP core and just use

It will be still the same, have to try to look for nodes by:

Timing analyzer -> Constrain -> set_multiclycle_path -> select the nodes

any further queries?

Yes, how does set_multicycle_path help me do my path analysis correctly?

I think multicycle is just being given as an example of accessing one of the GUI dialog boxes to access the Name Finder tool. There's no way to search for nodes in the timing netlist without going through one of these dialog boxes and I guess multicycle was selected just as an example. You don't need multicycle for the design.

Can you describe more on the previous question?

Once you set multicylce, you should be able to open up timing analyzer to analyze for that path.

any update?

Ok, how to describe this multiplexer correctly? But "my module" must be used in different projects, and i don't know whats clocks used on "Tol level"

Usually, Multiplexer does not consist of a clock. Does your Mux have a clock? If no, you do not need to set any clock for it. Timing analyzer analyze the path from register to register, once you have a register, you should have a clock to be constraint.

My multiplexer switches the clock. And to describe it, you need to describe the clock groups

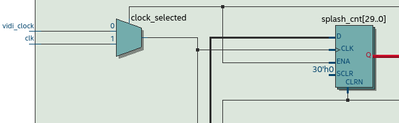

Is this the multiplexer that you are working at?

yes, but clkA and clkB on Top, to which I have no access and I do not know anything about it