- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

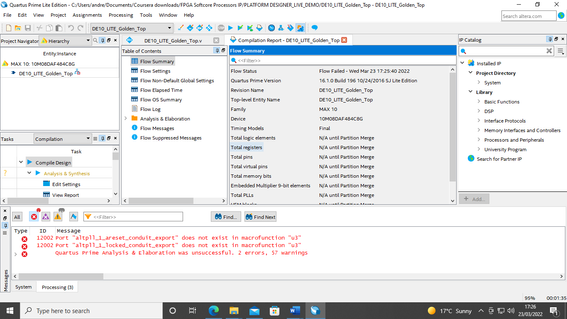

I create a NIOS 2 processor in platform designer 18.1 and then transferred into a Verilog file and then I do the following below in Quartus prime lite edition18.1.

- (double click) core(dir)

- (select) core_inst.v

- (click) Open

- Template to instantiate

- Select All: Copy

- Open: DE10_LITE_Golden_Top.v

- Past Core: change u0 to u3

When I do start analysis and elaboration I get the this error

Error (12006): Node instance "u3" instantiates undefined entity "core". Ensure that required library paths are specified correctly, define the specified entity, or change the instantiation. If this entity represents Intel FPGA or third-party IP, generate the synthesis files for the IP.

If anyone could please help me out on this error?

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Did you add the .qip or .qsys file to your Quartus project (Project menu -> Add/Remove files in project)? Either way, your PD system file must be named core.qsys. core.qip will not be created unless you manually generate your PD system, so it's usually easier to just add the .qsys file to your project so the system gets generated every time you compile your project.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

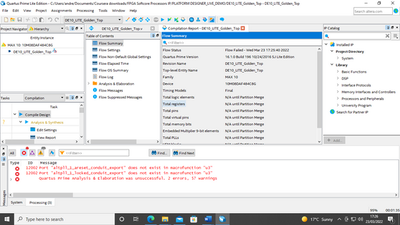

Thanks for the reply. I have tried adding the core.qsys with the DE10_LITE_Golden_Top Verilog as can be seen below but still no luck as the following error messages get shown when compilation is finished. Let me know if anyone knows the solution?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Do you have any further update or concern?

Thanks,

Sheng

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for the reply. I have tried adding the core.qsys with the DE10_LITE_Golden_Top Verilog as can be seen below but still no luck as the following error messages get shown when compilation is finished. Let me know if anyone knows the solution?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Can you show your Platform Designer system? Something is simply not connected correctly.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am trying to send the core.qsys file through but the file format is not supported through the forum. how is the best way to send the file?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It'll be easier if you upload a zip, qar, tar, 7z or rar file.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have posted a .rar file with the files. Let me if you know the solution?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have posted a .rar file with the files. Let me if you know the solution?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Below are the instantiations of core u3 in DE10_LITE_Golden_Top.v :

.altpll_0_c1_c1k ( ),

.altpll_1_areset_conduit_export (ARDUINO_IO[2]),

.altpll_1_locked_conduit_export (ARDUINO_IO[3])

As sstrell mentioned earlier, this is interconnection problem. I don't see ports above altpll_0_c1_c1k, altpll_1_areset_conduit_export and altpll_1_locked_conduit_export being instantiated in core.v as well as core_inst.v. May be you have to check again. There is no error at altpll_0_c1_c1k because it is not being connected yet.

Thanks,

Best regards,

Sheng

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution and give Kudos.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Do you have any further update or should I consider the case closed?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Since there are no further feedback for this thread, I shall set this thread to close pending. If you still need further assistance, you are welcome reopen this thread within 20days or open a new thread, some one will be right with you.