- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

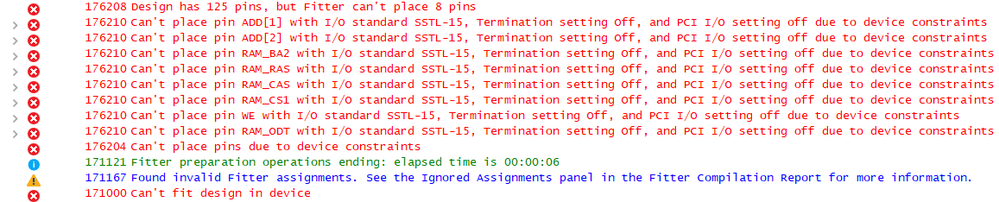

I have a "DDR3 SDRAM Controller with UniPHY Intel FPGA IP" instantiated on its own in a design with no other logic. When I compile the fitter is not able to place 8 pins. The error messages are in the image. The attached txt file has details.

When the fitter is at full liberty since I did not personally specify and pin location constrains, it is unable to fit all DDR3 pins into the banks 5 and 6. These are the only banks that can be used for DDR3 signals. Does this prove that DDR3 cannot be used with this device?

I am confused this DDR3 must be useable with the 10M16 range of MAX10 FPGAs but here the fitter fails.

The device used is the 10M16DAF256I6G.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What is the memory configuration/setup? The EMIF spec estimator for MAX 10 with DDR3 only indicates you can use only a single chip select, but you have CS1 in these errors. Fill in your info here to see:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Looks like the Pin assignments are incompatible for the following pins:

RAM_BA0

RAM_BA1

RAM_BA2

RAM_CAS

RAM_RAS

RAM_CS1

RAM_WE

RAM_ODT

These pins which need 1.5V are being assigned to Banks which are already configured for 1.2V . Check the pin assignments and change them to the proper Banks for 1.5V and compile. This should solve the issue.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page