- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

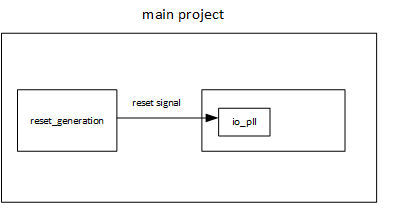

Hello I am working on a project containing several submodules. One of them contains a PLL that gets its reset signal from a reset generation block instantiated in the main project.

The problem is that when I try to compile my project wth Quartus, I get the error mesage "rst_n port on the pll is not properly connected". However, the pll reset is connected in my design.

I am working on a design for ARRIA 10 FPGA.

best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am sorry for not updating my case. Actually, I have found an error in my reset generation bloc that makes the reset signal always stuck on '0'. Thus, the synthesis tool, makes his optimisation process by deleting the reset bloc with other design parts. Then it considers that the reset signal of the PLL is not connected which generates this error message.

Thank you for your help.

Best regards,

Lotfi.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you post your RTL code to verify you've made the connection correctly?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you please check the below solution & old thread?

https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/component/2017/14--why-do-i-see-the-error-error--rstn-port-on-the-pll-is-not-pr.html

https://forums.intel.com/s/question/0D50P00003yySnZSAU/reset-for-pll

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am sorry for not updating my case. Actually, I have found an error in my reset generation bloc that makes the reset signal always stuck on '0'. Thus, the synthesis tool, makes his optimisation process by deleting the reset bloc with other design parts. Then it considers that the reset signal of the PLL is not connected which generates this error message.

Thank you for your help.

Best regards,

Lotfi.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page