- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

I am trying to connect DDR4 with my Arria 10 FPGA with the help of EMIF IP. I had gone through the example design. I had followed the complete steps from Example Guide for building the example design, also i got the waveforms in Signal Tap analyzer but those waveforms shows the Transactions between Traffic Generator and EMIF IP. I want to see the waveforms of data transfer between EMIF and DDR4. Please help me with this.

My main aim is to see the data transfer between FPGA and External Memory(DDR4) through EMIF IP.

Thanks a lot for your help.

Regards,

M A Muneeb

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can't use Signal Tap for this since those are hardened paths to the I/O. Enable the use of the EMIF Debug Toolkit in your example design to help test and debug that part of the interface.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your reply.

Yes i tried enabling the EMIF Debug Toolkit. In the EMIF Debug toolkit also, it says all the calibration tests pass. But i am not able to find the place where i could see the required signals. Could you please help me debug with EMIF Debug Toolkit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you sir for your reply.

Sorry for bothering again and again.

what do you mean by seeing them in a simulation ? (Do you mean Modelsim Simulations?)

Could you please tell the steps to see the signals in simulation.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I can see that you have mark this thread as solved. I will transition this thread to community support.

Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you.

After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

Thank you.

-Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sir,

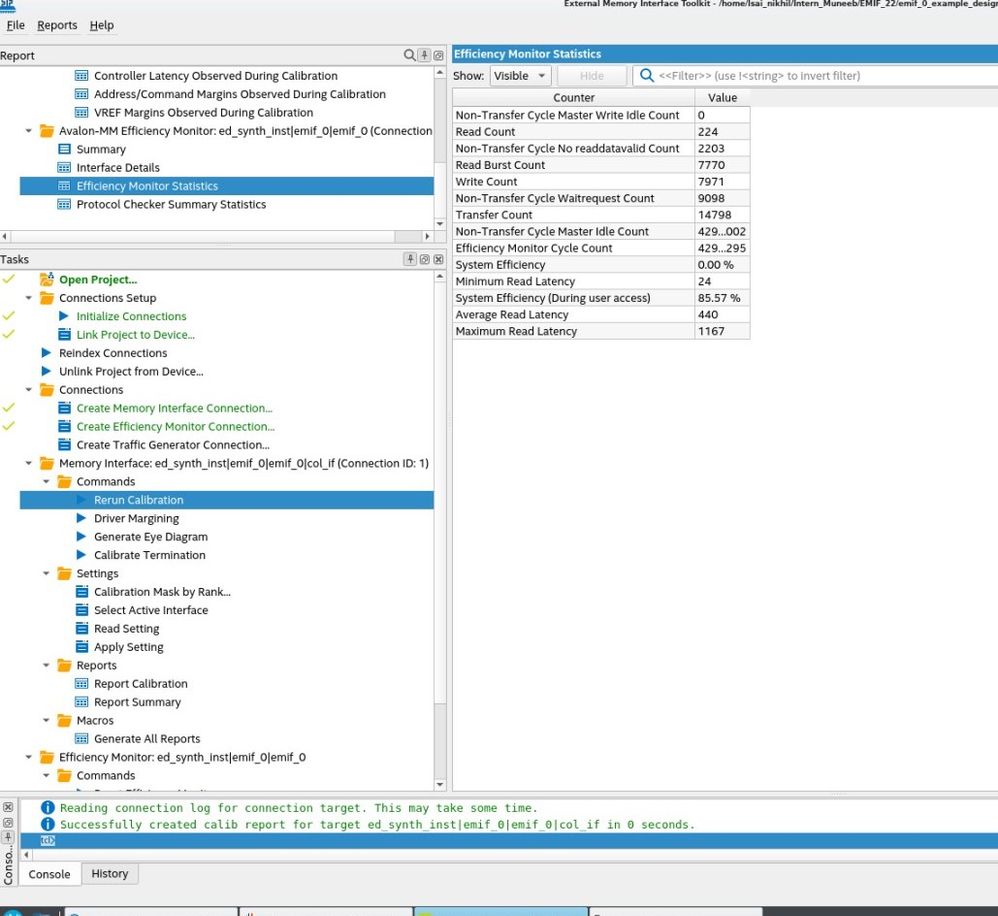

I have been provided with references that allowed me to view the PNF bits in the Signal Tap Logic Analyzer. Additionally, I have obtained some data from the Efficiency Monitor using the EMIF Debug Toolkit (as shown in the attached snapshot). However, I am currently unable to determine the speed of data transfer between the FPGA and DDR4 memory, specifically the speed of reads or writes. I am seeking assistance in this matter. Please help me with this.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page