- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

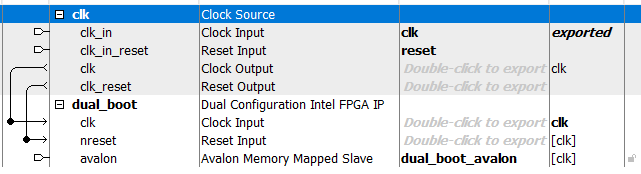

I use altera_dual_boot (Dual Configuration) IP core without Nios II. I use the IP core for RSU implement. I can write the writable registers with addresses [0,1] (Trigger reconfig and config selection registers). But I cannot read the read only registers such as addresses [3,7] (Busy state and config selection info registers). When I try the read them, I get 0. I though they are really be 0 but I change the config sel reg and read after that, it still give me 0. I know I successfully change the config sel because I can reconfig from the selected CFM.

By the way they are not any documentation about how can we read or write the data to this regs. IP core's document (ug_m10_config) just tells the regs addresses. In the platform designer, I export the dual boot IP pin to control it over VHDL. The exported pins are {address, read, write, read_address, write_address}. I assume the read and write signals are for enabling these operations.

In the VHDL code, I use these signals like:

Component definition:

component pdesigner is

port(

clk_clk: in std_logic:= 'X'; -- clk

reset_reset_n: in std_logic:= 'X'; -- reset_n

dual_boot_avalon_address: in std_logic_vector(2 downto 0):= (others => 'X'); -- address

dual_boot_avalon_read: in std_logic:= 'X'; -- read

dual_boot_avalon_writedata: in std_logic_vector(31 downto 0):= (others => 'X'); -- writedata

dual_boot_avalon_write: in std_logic:= 'X'; -- write

dual_boot_avalon_readdata: out std_logic_vector(31 downto 0) -- readdata

);

end component;

Port mapping:

rsu_block : component pdesigner

port map (

clk_clk => clk,

reset_reset_n => reset,

dual_boot_avalon_address => db_avalon_address,

dual_boot_avalon_read => db_avalon_read,

dual_boot_avalon_writedata => db_avalon_writedata,

dual_boot_avalon_write => db_avalon_write,

dual_boot_avalon_readdata => db_avalon_readdata

);

RTL:

cnt <= cnt + 1;

if(cnt = 0) then

db_avalon_address <= "011"; -- rsu busy reg

db_avalon_write <= '0';

db_avalon_read <= '1';

elsif(cnt = 5) then

db_avalon_write <= '0';

db_avalon_read <= '0';

LED(0) <= db_avalon_readdata(0); -- rest of them is reserved

elsif(cnt = 10) then

db_avalon_address <= "001";

db_avalon_writedata(0) <= '1'; -- set config_sel_overwrite

db_avalon_writedata(1) <= boot_cfm_sel; -- set config_sel

db_avalon_writedata(31 downto 2) <= (others => '0'); -- reserved

db_avalon_write <= '1';

elsif(cnt = 15) then

db_avalon_write <= '0';

db_avalon_address <= "111"; -- config sel input reg

db_avalon_read <= '1';

elsif(cnt = 20) then

db_avalon_write <= '0';

db_avalon_read <= '0';

LED(1) <= db_avalon_readdata(0);

elsif(cnt = 25) then

db_avalon_address <= "000"; -- trigger reconfig

db_avalon_writedata <= x"00000001"; -- hold nconfig min 250ns, 4 cycle at 12 MHz

db_avalon_write <= '1';

else

end if;

So with this code, I can write and reconfig but cannot read the registers. Any help will be appreciated.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The read signal is active high. Why are you setting db_avalon_read to 0 when you're trying to do a read? The read signal must be held with the address to perform a read.

I'm presuming this is a clocked process for the cnt signal.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes this is clocked process, I don't want to bother you with legwork. I'm setting the db_avalon_read high for 5 cycles then I clear it. My measurement show me that 3 cycles are enough for read / write. I changed my code a little bit and I can read the busy signal but still no data at config sel reg. Here is my edited code:

if(cnt = 0) then

db_avalon_address <= "001";

db_avalon_writedata(0) <= '1'; -- set config_sel_overwrite

db_avalon_writedata(1)<= boot_cfm_sel; -- set config_sel

db_avalon_writedata(31 downto 2) <= (others => '0'); -- reserved

db_avalon_write <= '1';

db_avalon_read <= '0';

cnt <= cnt + 1;

elsif(cnt = 3) then -- write operation needs 3 cycle

db_avalon_write <= '0';

db_avalon_read <= '0';

cnt <= cnt + 1;

elsif(cnt = 4) then

db_avalon_address <= "011"; -- busy reg

db_avalon_read <= '1';

db_avalon_write <= '0';

cnt <= cnt + 1;

elsif(cnt = 5) then -- read operation needs 1 cycle

db_avalon_read <= '0';

db_avalon_write <= '0';

cnt <= cnt + 1;

elsif(cnt = 6) then -- read data came in 2th cycle

if(db_avalon_readdata /= x"00000000") then

LED(0) <= db_avalon_readdata(0);

cnt <= 4;

else

cnt <= cnt + 1;

end if;

elsif(cnt = 20000000) then

db_avalon_address <= "000"; -- trigger reconfig

db_avalon_writedata <= x"00000001"; -- hold nconfig min 250ns, 4 cycle at 12 MHz

db_avalon_write <= '1';

db_avalon_read <= '0';

cnt <= cnt + 1;

else -- wait for FPGA trig reconfig

cnt <= cnt + 1;

end if; - Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't see you accessing address 7 at all in this revised code.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can think that the address 3 in the revised code as address 7. Because I tried both addresses.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page